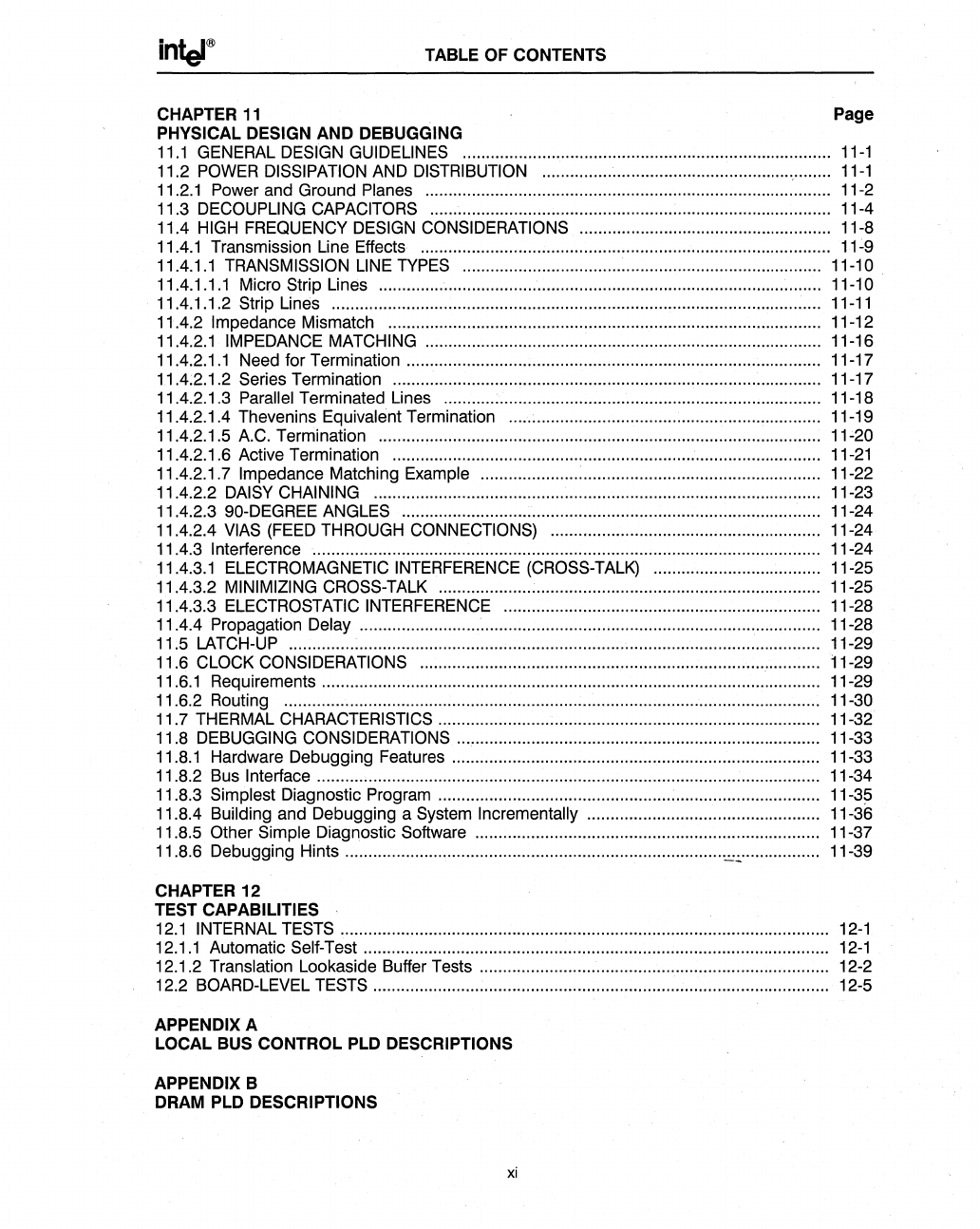

TABLE

OF CONTENTS

CHAPTER

11

Page

PHYSICAL DESIGN AND DEBUGGING

11.1

GENERAL DESIGN GUIDELINES ...............................................................................

11-1

11.2 POWER DISSIPATION AND DISTRIBUTION ..............................................................

11-1

11.2.1

Power and Ground Planes .......... ............

....

........ ................................. ................ .... 11-2

11.3 DECOUPLING

CAPACITORS ...................................................................................... 11-4

11.4

HIGH FREQUENCY DESIGN CONSIDERATIONS ...................................................... 11-8

11.4.1

Transmission Line Effects ..................... ....... ...................

...

....

........... ........ ......

...

...... 11-9

11.4.1.1

TRANSMISSION LINE

TYPES

............................................................................. 11-10

11.4.1.1.1 Micro Strip Lines .... ................ ............ ............ ............ ....... ................... ......... .... 11-10

11.4.1.1.2 Strip Lines ........................................................................ , ................................

11-11

11.4.2 Impedance Mismatch ............................................................................................. 11-12

11.4.2.1

IMPEDANCE MATCHING ..................................................................................... 11-16

11.4.2.1.1 Need for Termination ......................................................................................... 11-17

11.4.2.1.2 Series Termination ............................................................................................ 11-17

11.4.2.1.3

Parallel Terminated Lines ................................................................................. 11-18

11.4.2.1.4 Thevenins Equivalent Termination ....

...

........................

....

............ .............

...

.... 11-19

11.4.2.1.5 A.C. Termination ...............................................................................................

11-20

11.4.2.1.6 Active Termination ............................................................................................

11-21

11.4.2.1.7 Impedance Matching Example ......................................................................... 11-22

11.4.2.2

DAISY CHAINING ................................................................................................ 11-23

11.4.2.3 90-DEGREE ANGLES ........... .......................... ....... ..... .............. ......... ............ ...... 11-24

11.4.2.4

VIAS

(FEED THROUGH CONNECTIONS) .......................................................... 11-24

11.4.3 Interference.... ......

....

...

...............

...

.................. ..... ............... ................ ............. ....... 11-24

11.4.3.1

ELECTROMAGNETIC INTERFERENCE (CROSS-TALK) .................................... 11-25

11.4.3.2

MINIMIZING CROSS-TALK .................................................................................. 11-25

11.4.3.3

ELECTROSTATIC INTERFERENCE .................................................................... 11-28

11.4.4 Propagation Delay...................................................................................... ............. 11-28

11.5 LATCH-UP .................................................................................................................. 11-29

11.6

CLOCK CONSIDERATIONS ...................................................................................... 11-29

11.6.1

Requirements ..... ..... ....... ....... ....... ......... ..........................

...

.............

...

....

...

.........

... ...

11-29

11.6.2 Routing ...... ........ ......... ..................................... ............ ....... ....... .............................

11-30

11.7 THERMAL CHARACTERISTICS ....................................... ....... ....... ............................. 11-32

11.8

DEBUGGING CONSIDERATIONS .............................................................................. 11-33

11.8.1 Hardware Debugging Features ............................. ............................ ....... ............... 11-33

11.8.2 Bus

Interface ............................................................................................................ 11-34

11.8.3 Simplest Diagnostic Program ........ ............

...

....

................. ........... ........................... 11-35

11.8.4 Building and Debugging a System

Incrementally..... .............. ......... ...................... 11-36

11.8.5 Other Simple Diagnostic Software

...

....................................... .......

...

....

...............

...

11-37

11.8.6 Debugging Hints .................................................................................

'-'.:.:..

............... 11-39

CHAPTER 12

TEST

CAPABILITIES

12.1

INTERNAL TESTS .........................................................................................................

12-1

12.1.1

Automatic Self-Test

..

................ ...... .......... ..... ......... ............ ............................ ........ ....

12-1

12.1.2 Translation Lookaside Buffer Tests ........................................................................... 12-2

12.2 BOARD-LEVEL

TESTS ....... ......................... ..... ............

....

..... .............................. .......... 12-5

APPENDIX A

LOCAL BUS CONTROL

PLD

DESCRIPTIONS

APPENDIX

B

DRAM

PLD

DESCRIPTIONS

xi