SYSTEM OVERVIEW

Table

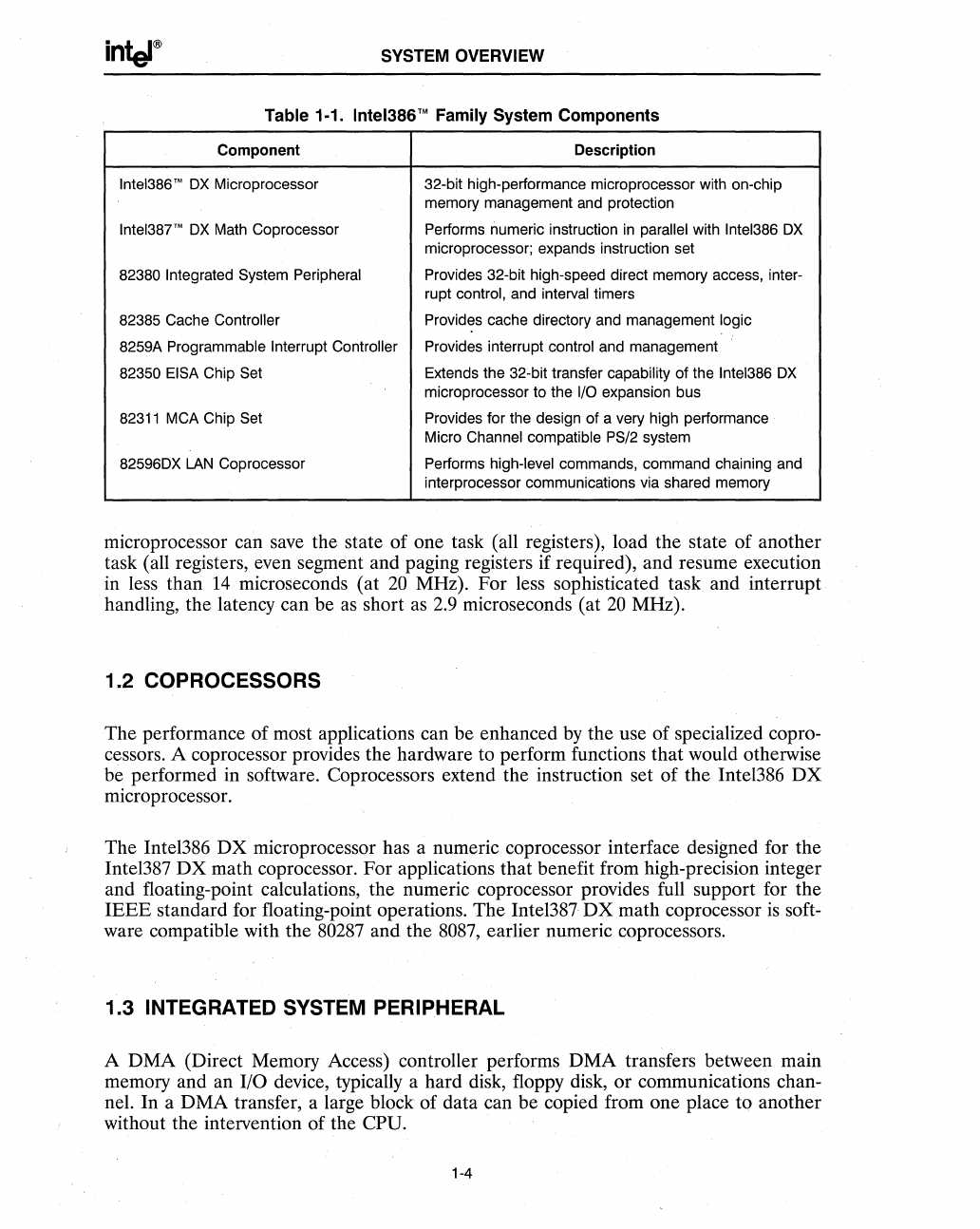

1-1. Intel386™ Family System Components

Component

Description

Inte1386'M

OX

Microprocessor

32-bit high-performance microprocessor with on-chip

memory management and protection

Intel38TM

OX

Math Coprocessor Performs numeric instruction in parallel with Intel386

OX

microprocessor; expands instruction set

82380 Integrated System Peripheral Provides 32-bit high-speed direct memory access, inter-

rupt

control, and interval timers

82385 Cache

Controller Provides cache directory and management logic

8259A Programmable Interrupt Controller Provides interrupt control and management

82350 EISA Chip Set Extends the

32~bit

transfer capability

of

the Intel386

DX

microprocessor to the I/O expansion bus

82311 MCA Chip Set Provides for the design

of

a very high performance

Micro

Channel compatible PS/2 system

825960X

LAN

Coprocessor Performs high-level commands, command chaining and

interprocessor communications via shared memory

microprocessor can save the state of one task (all registers), load the state of another

task (all registers, even segment and paging registers if required), and resume execution

in less than

14

microseconds (at

20

MHz). For less sophisticated

task

and interrupt

handling, the latency can be

as

short

as

2.9

microseconds (at

20

MHz).

1.2 COPROCESSORS

The performance of most applications can be enhanced

by

the use of specialized copro-

cessors. A coprocessor provides the hardware to perform functions that would otherwise

be performed in software. Coprocessors extend the instruction set of the Intel386

DX

microprocessor.

The Intel386

DX

microprocessor has a numeric coprocessor interface designed for· the

Inte1387

DX

math coprocessor. For applications that benefit from high-precision integer

and floating-point calculations, the numeric coprocessor provides full support for the

IEEE

standard for floating-point operations. The Intel387

DX

math coprocessor

is

soft-

ware compatible with the

80287

and the

8087,

earlier numeric coprocessors.

1.3 INTEGRATED SYSTEM PERIPHERAL

A DMA (Direct Memory Access) controller performs DMA transfers between main

memory and an

I/O device, typically a hard disk, floppy disk, or communications chan-

nel.

In

a DMA transfer, a large block of data can be copied from one place to another

without the intervention of the

CPU.

1-4