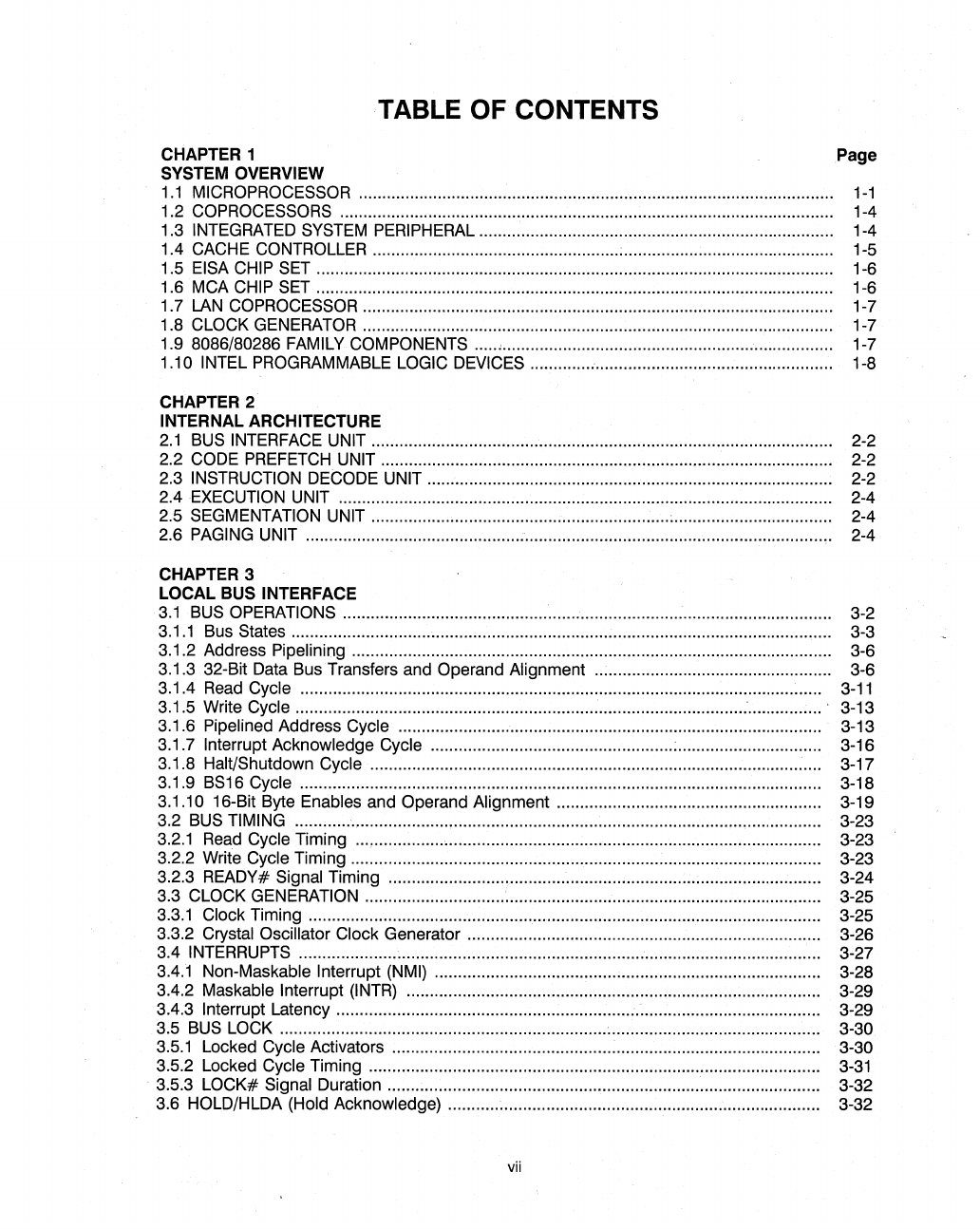

TABLE

OF

CONTENTS

CHAPTER 1

Page

SYSTEM OVERVIEW

1.1

MICROPROCESSOR ......................................................................................................

1-1

1.2 COPROCESSORS ...............................................................................

'"

..... ....

....

...

........ 1-4

1.3

INTEGRATED SYSTEM PERIPHERAL ............................................................................ 1-4

1.4 CACHE CONTROLLER ..................................................... :............................................. 1-5

1.5

EISA CHIP SET ............................................................................................................... 1-6

1.6 MCA

CHIP SET ............................................................................................................... 1-6

1.7

LAN

COPROCESSOR

..

...... ....... ...... ..... ..... ....

...

....... ..... .... ..... ....... ....... ........ .... ..... ...... ..... 1-7

1.8 CLOCK GENERATOR ..................................................................................................... 1-7

1.9 8086/80286

FAMILY COMPONENTS .....•....................................................................... 1-7

1.10

INTEL PROGRAMMABLE LOGIC DEVICES ............. :................................................... 1-8

CHAPTER 2

INTERNAL ARCHITECTURE

2.1

BUS INTERFACE UNIT ................................................................................................... 2-2

2.2 CODE

PRE

FETCH UNIT ..... ....... .... ..... ..... ..... ......... ..... .... ....... ..... ......•.... ..... .....

....

........

...

2-2

2.3

INSTRUCTION DECODE UNIT ....................................................................................... 2-2

2.4

EXECUTION UNIT ....................................................................................•..................... 2-4

2.5

SEGMENTATION UNIT ................................................................ ;.................................. 2-4

2.6

PAGING UNIT ...............................................................................................................•. 2-4

CHAPTER 3

LOCAL

BUS INTERFACE

3.1

BUS OPERATIONS ......................................................................................................... 3-2

3.1.1 Bus States

..

.... ..... ......... ..... .... ...... .... ..... .... ..... ......... .....

...

........ ........ ..... ......... ......

...

....... 3-3

3.1.2 Address

Pipelining ....................................................................................................... 3-6

3.1.3 32-Bit Data Bus Transfers and Operand

Alignment

..

:................................................ 3-6

3.1.4 Read

Cycle

..

..... .... ..... .......... ......... ....... ..... ..... .... ..... .....

...

.... .............. .... ....

...

....

...

.......

3-11

3.1.5 Write Cycle ................................................................................................ : ................. 3-13

3.1.6

Pipelined Address Cycle ..... ..... .... .....

...

......... ..... ......

...

..... .... ..... ............. .... ..... ..... ..... 3-13

3.1.7

Interrupt Acknowledge Cycle .................................................... : ............................... 3-16

3.1.8

Halt/Shutdown Cycle ............................................................................................ :.... 3-17

3.1.9

BS16 Cycle ................................................................................................................ 3-18

3.1

.10 16-Bit Byte Enables and Operand Alignment .....

...

......... ............. ..... .... ..... ......... .... 3-19

3.2

BUS TIMING ............

~

.................... ,............................................................................... 3-23

3.2.1

Read Cycle Timing

...

, ............... ,................................................................................ 3-23

3.2.2 Write

Cycle Timing ....... .... .... ........ ..... ....... ..... ..... .... ..... .... ..... ....................... ......... ...... 3-23

3.2.3 READY#

Signal Timing ............................................................................................. 3-24

3.3 CLOCK

GENERATION ................................................................................................... 3-25

3.3.1

Clock Timing ................................................ ,............................................................. 3-25

3.3.2

Crystal Oscillator Clock Generator

... ...

......... ..... ......... .....

...

..... ........ .......... ...... ..... ..... 3-26

3.4

INTERRUPTS ..................... :.......................................................................................... 3-27

3.4.1

Non-Maskable Interrupt (NMI) ................................................................................... 3-28

3.4.2

Maskable Interrupt (INTR) ......................................................................................... 3-29

3.4.3

Interrupt Latency ................................................................. :....................................... 3-29

3.5

BUS LOCK ...................................................................... ;............................................. 3-30

3.5.1

Locked Cycle Activators

..

...... ............

...

....

...

..... ..... ...... ..... ..... ......... .... ..... ....... .....

... ...

3-30

3.5.2 Locked

Cycle Timing .................................................................................................

3-31

. 3.5.3 LOCK# Signal Duration

'"

....... .... ...... .... ............ ..... ..... .... ..... ...... ....... .......

...

............... 3-32

3.6 HOLD/HLDA

(Hold Acknowledge) ................................................................................ 3-32

vii