I\)

CiJ

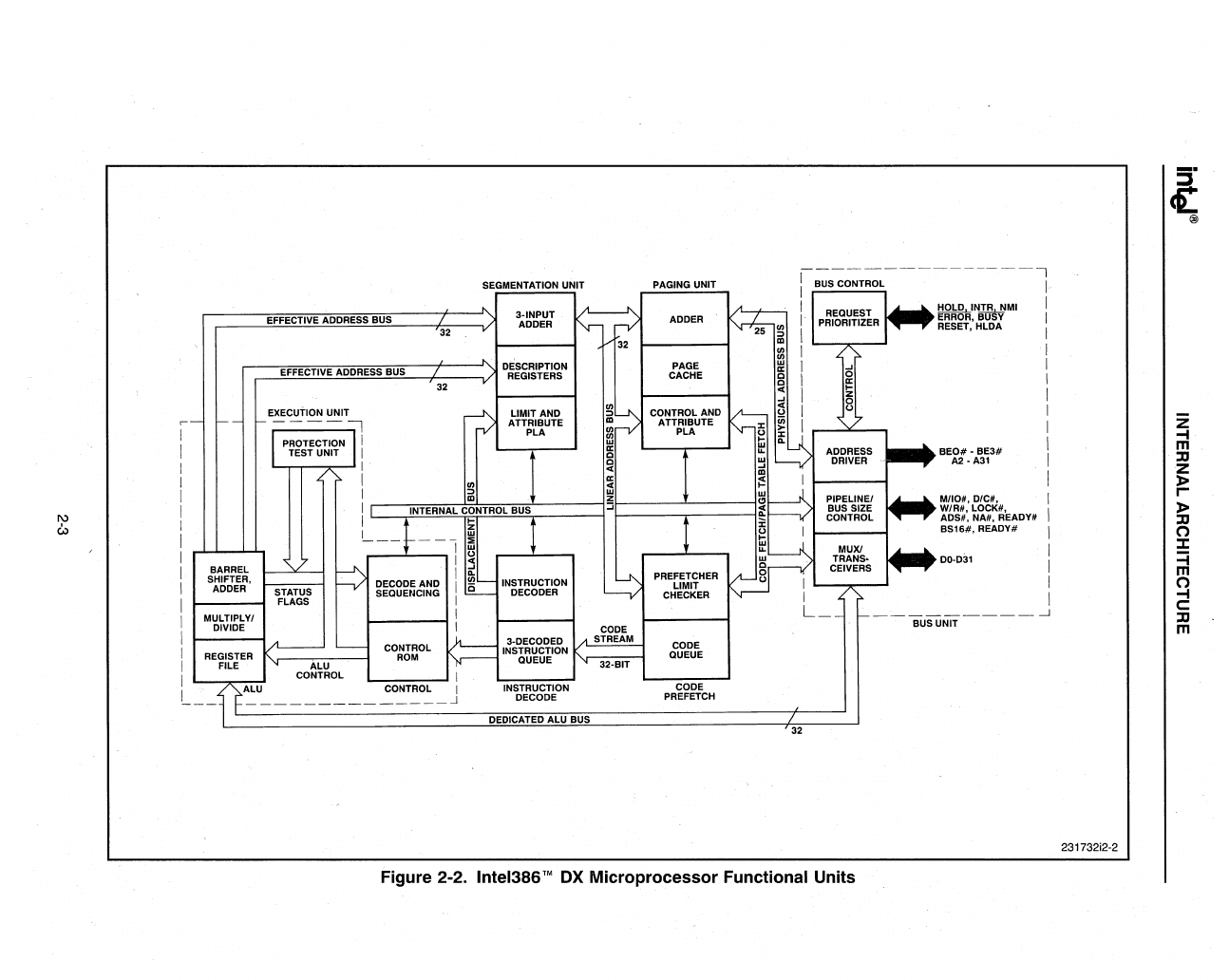

SEGMENTATION UNIT

PAGING UNIT

i i

EFFECTIVE ADDRESS BUS

3-INPUT

~~~gR~N~MI

ADDER RESET. HLDA

--l

1--

BARREL

32

EFFECTIVE ADDRESS

BUS

/ JI

D~SCRIPTION

; REGISTERS

EXECUTION

UNIT

----::::-1

I

I

L-,.-,-_",-'

I

I

I

32

?

LIMIT AND

ATTRIBUTE

PLA

I

....-----,==~

I

L--r'"'-=="--~=~

L

__

SHIFTER. INSTRUCTION

ADDER STATUS DECODER

I FLAGS

I

M~~Jlb~YI

I 3-DECODED

I REGISTER .

CO:J:

OL

INS~~~~110N

~

I FILE

CO~~~OL

I

I ALU CONTROL I INSTRUCTION

l__

_

_____________

.J DECODE

DEDICATED

ALU BUS

PAGE

CACHE

32

...I

~

8

Figure 2-2. Intel386™

OX

Microprocessor Functional Units

BEO# -

BE3#

A2-A31

M/IOH.

D/CH.

W/RH.

LOCKH.

ADSH.

NAH.

READYH

BSI6#.

READY#

DO-D31

_________

---.J

BUS UNIT

231732i2-2

l

@l

Z

-I

m

::D

z

»

.-

»

::D

n

::I:

=i

m

~

c:

::D

m