I/O INTERFACING

In Intel386 DX microprocessor systems, the instructions that provide recovery time are

executed more quickly than in earlier systems. For software compatibility with earlier

microprocessor generations, hardware must guarantee the recovery time. However, the

circuitry to delay bus commands selectively for the specific instance

of

back-to-back

accesses to a particular device

is

typically more complex than the frequency of such

accesses justifies. Therefore, the preferred solution

is

to delay all I/O cycles

by

the

minimum recovery time. Because most

I/O accesses are relatively infrequent, perfor-

mance

is

not degraded.

Only two peripherals do not meet the bus controller specifications: the

8041

and

8042

UPls (Universal Peripheral Interface 8-bit Microcomputers). These intelligent peripher-

als meet all but the command recovery specification,

so

they can be used if this delay

is

implemented in software.

8.5 BASIC I/O EXAMPLES

In this section,

two

examples of the interface to slave I/O devices are presented. Typi-

cally, several of these devices exist on the Intel386

DX

microprocessor local bus. The

. basic I/O interface presented above

is

used for both examples.

8.5.1 8274 Serial Controller

The

8274

Multi-Protocol Serial Controller (MPSC)

is

designed to interface high-speed

serial communications lines using a variety of communications protocols, including

asyn-

chronous, IBM bisynchronous, and HDLC/SDLC protocols. The

8274

contains two inde-

pendent full-duplex channels and can serve

as

a high-performance replacement for

two

8251A Universal Synchronous/Asynchronous Receiver Transmitters (USARTs).

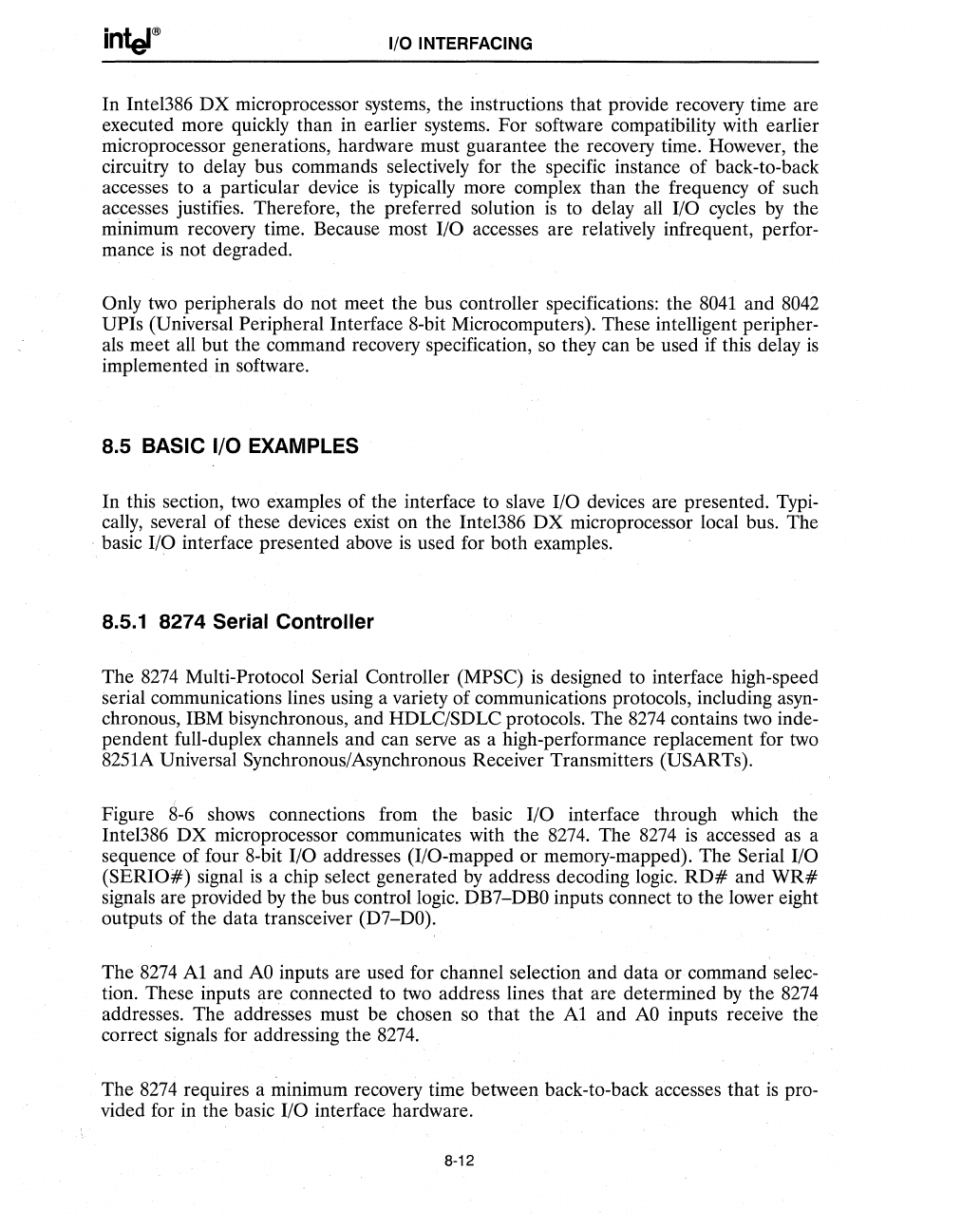

Figure

8-6

shows connections from the basic I/O interface through which the

Intel386 DX microprocessor communicates with the

8274.

The

8274

is

accessed

as

a

sequence of four 8-bit

I/O addresses (I/O-mapped or memory-mapped). The Serial I/O

(SERIO#)

signal

is

a chip select generated

by

address decoding

logic.

RD#

and

WR#

signals are provided

by

the bus control logic. DB7-DBO inputs connect to the lower eight

outputs of the data transceiver (D7-DO).

The 8274

Al

and

AO

inputs are used for channel selection and data or command selec-

tion. These inputs are connected to

two

address lines that are determined

by

the

8274

addresses. The addresses must be chosen so that the

Al

and

AO

inputs receive the

correct signals for addressing the

8274.

The

8274

requires a minimum recovery time between back-to-back accesses that

is

pro-

vided for in the basic

I/O interface hardware. .

8-12