ClK2

IDLE

DRAM

READ

BANK 0 I

DRAM

READ

BANK 1

DRAM WRITE BANK 1 DRAM REFRESH

NON·PIPEUNED PIPEUNED

PIPELINED

(ALWAYS BOTH BANKS)

1234123

1 2 3 4 I 5 1 2 3 4 5

~

~JV\I\.~[v\.

'V\.~~

'V\.

'V\.~~rv"-

~l\lVV\I\,~~

ClK

Y Y

\J"

Y

~

\J"

Y Y

\J" \J"

\J"

Y

V

\.FjV-

Y Y Y

ADS.

W>L

...J1iU

W-

...JJD

'<M..-

..1lD

~

~!

SELECT

ROWSEl

r

~

MUX

X X

ROW

COLUMN

ROW

COLUMN

ROW

COLUMN

REFRESH

RASO'

I

RAS1'

~

CASd

ex>

WEO

'-1\

lOW

ONLY

'ForlED

BYTJS

,

I

DATA

ALE:

REAr--1\

READ

WRITE

DT/R.

IREADY

r--

----,.

NAO

~

1"\

REFRED

MUXOE'

'-

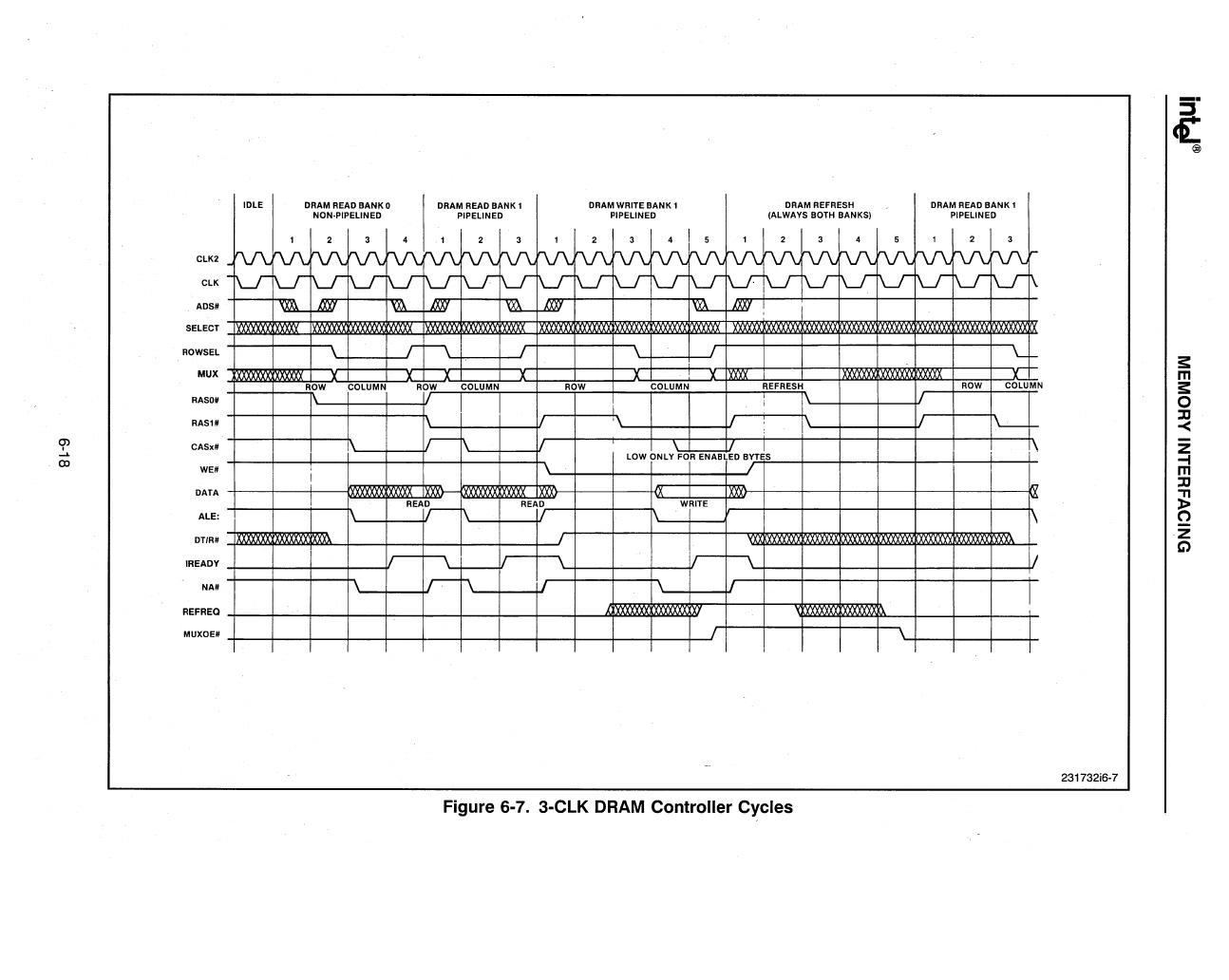

Figure 6-7.

3-ClK

DRAM Controller Cycles

DRAM

READ

BANK 1

PIPELINED

~~I~r

V

\J"

\J"[\

'--e-

X

ROW

CQlUMP

'-----

-

,\

\

J

I

I

23173216-7

l

!:

m

!:

o

::D

-<

Z

-I

m

::D

~

Z

G)

<8