9-34 SA-1100

Developer’s Manual

System Control Module

9.5.7.2 Power Manager General Configuration Register (PCFR)

The PCFR contains bits used to configure various functions within the SA-1100. The OPDE bit, if

set, allows the 3.6864-MHz oscillator to be disabled during sleep mode. This bit is cleared on the

assertion of nRESET. The FP and FS bits control the state of the PCMCIA control pins and the

static memory control pins during sleep. The following table shows the bit-field definitions for this

register. The FO bit forces the SA-1100 to assume that the 32-kHz oscillator is stable instead of

waiting for the requisite 2–10 seconds using an internal counter. This function is primarily useful

for "warm" hardware resets where the oscillator is already stable when the processor comes out of

reset.

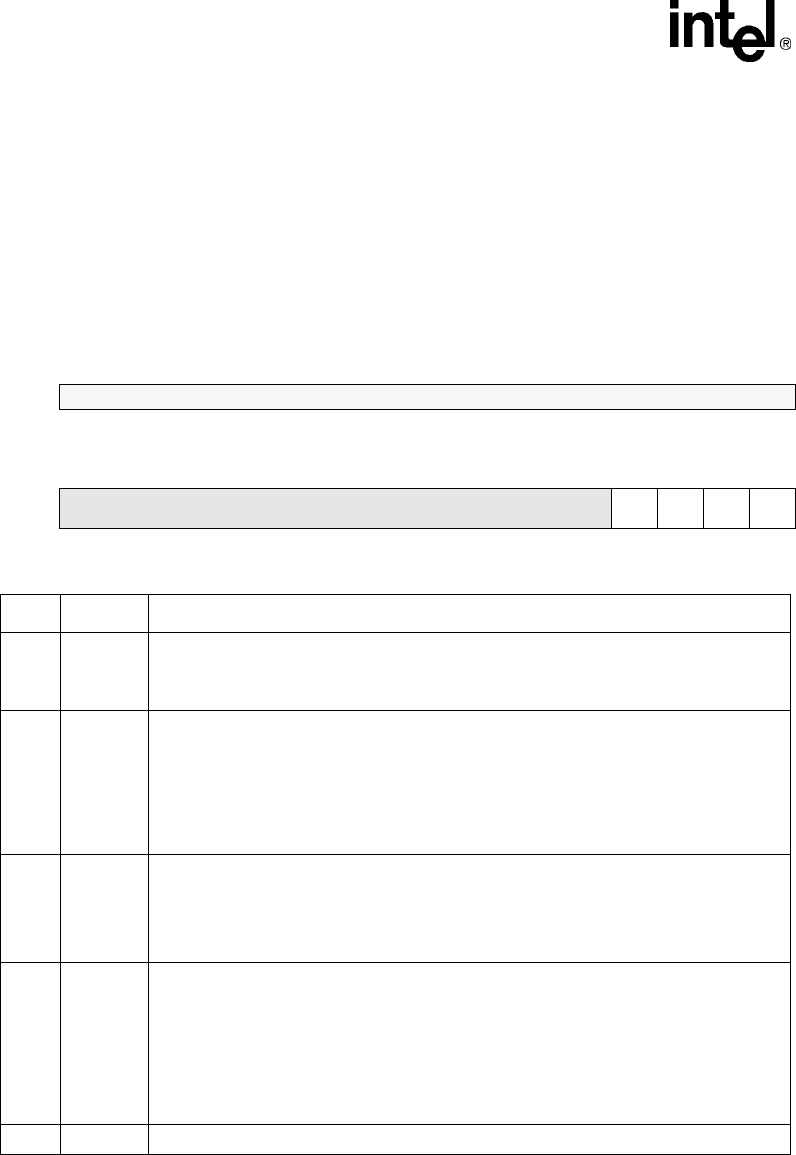

Bit31302928272625242322212019181716

R/W Reserved

Reset0000000000000000

Bit1514131211109876543210

R/W Reserved FO FS FP

OPD

E

Reset0000000000000000

Bit Name Description

0OPDE

3.6864-MHz oscillator power-down enable.

0 – Do not stop the oscillator during sleep mode (reset condition).

1 – Stop the 3.6-MHz oscillator during sleep mode.

1FP

Float PCMCIA controls during sleep mode.

This bit determines whether the PCMCIA control signals are driven to a high (negated)

state during sleep or not driven (floated). A zero indicates that the pins are driven low. A

one indicates that they will be floated. This bit is zero at hardware reset. The PCMCIA

signals affected by this bit are: nPOE, nPWE, nPIOW, nPIOR, nPCE<2:1>, nIOIS16,

and nPWAIT. PSKSEL and nPREG are derived from address signals and assume the

state of the address bus during sleep.

2FS

Float static chip selects during sleep mode.

This bit determines whether the static chip select control signals are driven to a high

during sleep or floated. A zero indicates that the pins are driven low. A one indicates that

they will be floated. The static chip select signals affected by this bit are: nCS<3:0>,

nOE, and nWE. This bit is zero at hardware reset.

3FO

Force 32-kHz oscillator enable on.

This bit is used to allow software to force the SA-1100 to use the 32-kHz oscillator for

internal clocking functions instead of waiting for it to stabilize in the normal way. This

function is

useful primarily to attain rapid functionality after a "warm" hardware reset when it is

known that the oscillator is stable. Use of this bit is intended for test purposes and

some

customer use in special situations. It should be used with care, however, since setting

this bit when the 32-kHz oscillator is not stable will yield unpredictable results.

31..4 — Reserved.