11-74 SA-1100

Developer’s Manual

Peripheral Control Module

11.8.10 UDC Endpoint 0 Data Register

The UDC endpoint 0 data register is actually an 8-bit x 8-entry bidirectional FIFO. When the host

transmits data to the UDC endpoint 0, the CPU reads the UDC endpoint 0 register to access the

data. When the UDC is sending data to the host, the CPU writes the data to be sent into the UDC

endpoint 0 register. Although the same FIFO can be read and written by the CPU during various

points in a control sequence, the CPU may not read and write the FIFO at the same time. The

direction that the FIFO is flowing is controlled by the UDC. Normally, the UDC will be in an idle

state, waiting for the host to send commands. When this happens, the UDC fills the FIFO with the

command from the host and the CPU reads the command from the FIFO once it has arrived. The

UDC will do a partial decode of the command to determine if the CPU is going to be filling the

FIFO with data to send to the host. If so, the direction is turned around to accept data from the CPU

and have the UDC transmit the data. If the command is such that no data will be required from the

UDC, then this will not happen. The only time the CPU may write the endpoint 0 FIFO is when a

valid command from the host has been received which requires a transmission in response, that is,

a GET_DESCRIPTOR command.

11.8.11 UDC Endpoint 0 Write Count Register

The UDC endpoint 0 write count register can be read when a packet has been received by the

endpoint 0 to determine how many bytes to read out of the UDC endpoint 0 data register. When

data is present in the FIFO, this 4-bit field should read between 1 and 8.

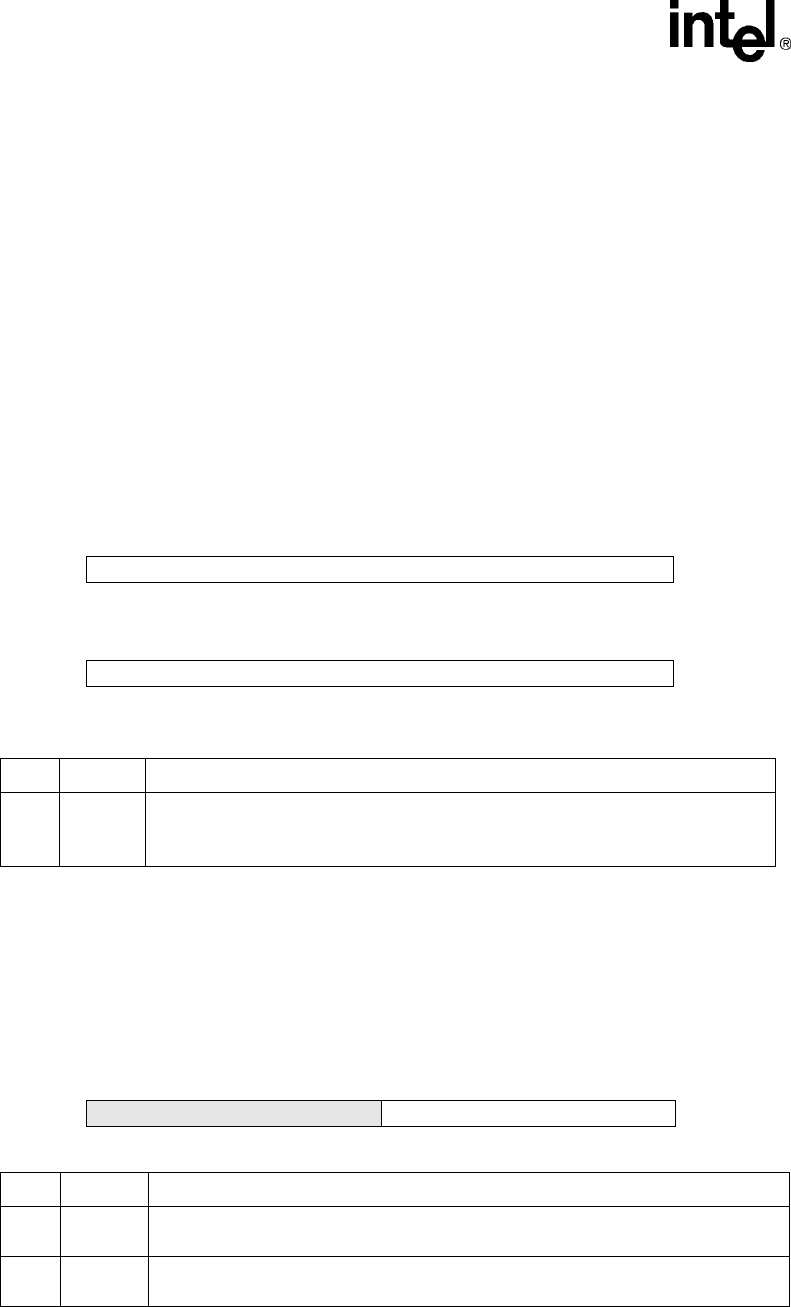

Address: 0h 8000 001C UDCD0 Read/Write

Bit76543210

Bottom of Endpoint 0 FIFO

Reset00000000

Read Access

Bit76543210

Top of Endpoint 0 FIFO

Reset00000000

Write Access

Bit Name Description

7..0 DATA

Top/bottom of endpoint 0 FIFO data.

Read – Bottom of endpoint 0 FIFO data.

Write – Top of endpoint 0 FIFO data.

Address: 0h 8000 0020 UDCWC Read-Only

Bit76543210

Reserved Write Count

Reset00000000

Bit Name Description

3..0 WC

Endpoint 0 write count (read-only).

4-bit field representing the number of bytes in the endpoint 0 FIFO.

7..4 —

Reserved.

Always reads zero.