11-80 SA-1100

Developer’s Manual

Peripheral Control Module

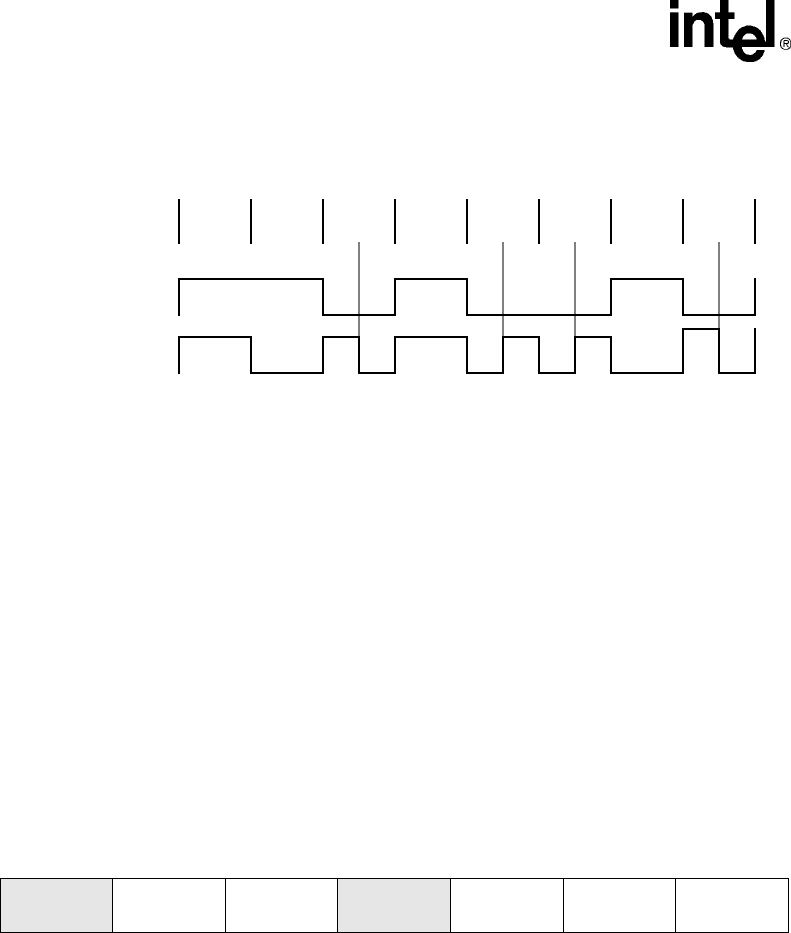

11.9.1.2 Frame Format

SDLC uses a flag (reserved bit pattern) to denote the beginning of a frame of information and to

synchronize frame transmission. The flag contains eight bits that start and end with a zero, and

contains six sequential ones in the middle (01111110). This sequence of six ones is unique because

all data between the start and stop flags is prohibited from having more than five consecutive ones.

Data that violates this rule is altered before transmission by automatically inserting a zero after five

consecutive ones are detected in the transmitted bit stream. This technique is commonly referred to

as “bit stuffing” and is transparent to the user. The information field within an SDLC frame is

placed between two flags and consists of an 8-bit address, an optional 8-bit control field, a data

field containing any multiple of 8 bits, and a 16-bit cyclic redundancy check (CRC-CCITT). The

user can also program the SDLC to insert an optional second start flag. Note that each byte within

the address, control, and data fields is transmitted and received LSB first, ending with the byte’s

MSB. However, the CRC is transmitted and received MSB first. Figure 11-23 shows the SDLC

frame format.

Figure 11-23. SDLC Frame Format

11.9.1.3 Address Field

The 8-bit address field is used by a transmitter to target a select group of receivers when multiple

stations are connected to the same set of serial lines. The address allows up to 255 stations to be

uniquely addressed (00000000 to 11111110). The global address (11111111) is used to broadcast

messages to all stations. Serial port 1 contains an 8-bit register that is used to program a unique

address for broadcast recognition. It also contains a control bit to enable or disable the address

match function. Note that the address of received frames is stored in the receive FIFO along with

normal data; it is transmitted and received starting with its LSB and ending with its MSB.

11.9.1.4 Control Field

The SDLC control field is typically 8 bits, but can be any length. Serial port 1 does not provide any

hardware decode support for the control byte; it treats all bytes between the address and the CRC as data.

Note that the control field is transmitted and received starting with its LSB and ending with its MSB.

Figure 11-22. FM0/NRZ Bit Encoding Example (0100 1011)

NRZ

Data

FM0

Data

Bit

Value

11010010

LSB

MSB

8 Bits

(optional)

8 Bits 8 Bits

8 Bits

(optional)

Any Multiple

of 8 Bits

16 Bits 8 Bits

Start Flag

0111 1110

Start Flag

0111 1110

Address

Control Data CRC-CCITT

Stop Flag

0111 1110