SA-1100 Developer’s Manual 10-13

Memory and PCMCIA Control Module

To calculate the recommended BS_xx value for each address space: divide the command width

time (the greater of twIOWR and twIORD, or the greater of twWE and twOE) by processor cycle

time; divide by 2; divide again by 3 (number of BCLKs per command assertion); round up to the

next whole number; and subtract 1. For example, for a processor cycle time of 6.25 ns and an

nIOWR command assertion time of 165 ns, the recommended setting for BS_IO would be

(165 /(2 x 3 x 6.25)) - 1 = 3.4, or 4 after rounding up.

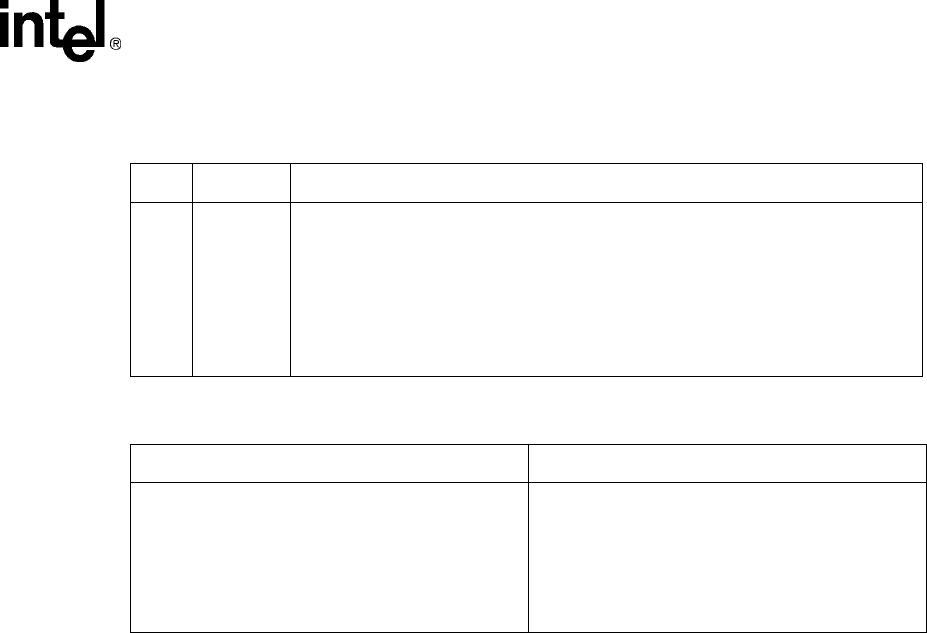

Table 10-3. BS_xx Bit Encoding

Bit Name Description

4..0 BS_xx 0b00000 – BCLK= 2 processor clocks (clk/2)

0b00001 – BCLK= 4 processor clocks

0b00010 – BCLK= 6 processor clocks

....

0b11101 – BCLK= 60 processor clocks

0b11110 – BCLK= 62 processor clocks

0b11111 – BCLK= 64 processor clocks

Table 10-4. BCLK Speeds for 160-MHz Processor Core Frequency

BCLK_SEL BCLK Cycle Time–ns

0b00000 – Every 2 processor clocks (clk/2).

0b00001 – Every 4 processor clocks.

0b00010 – Every 6 processor clocks.

0b00011 – Every 8 processor clocks.

...

0b11111 – Every 64 processor clocks.

12.5

25

37.5

50

400