11-8 SA-1100

Developer’s Manual

Peripheral Control Module

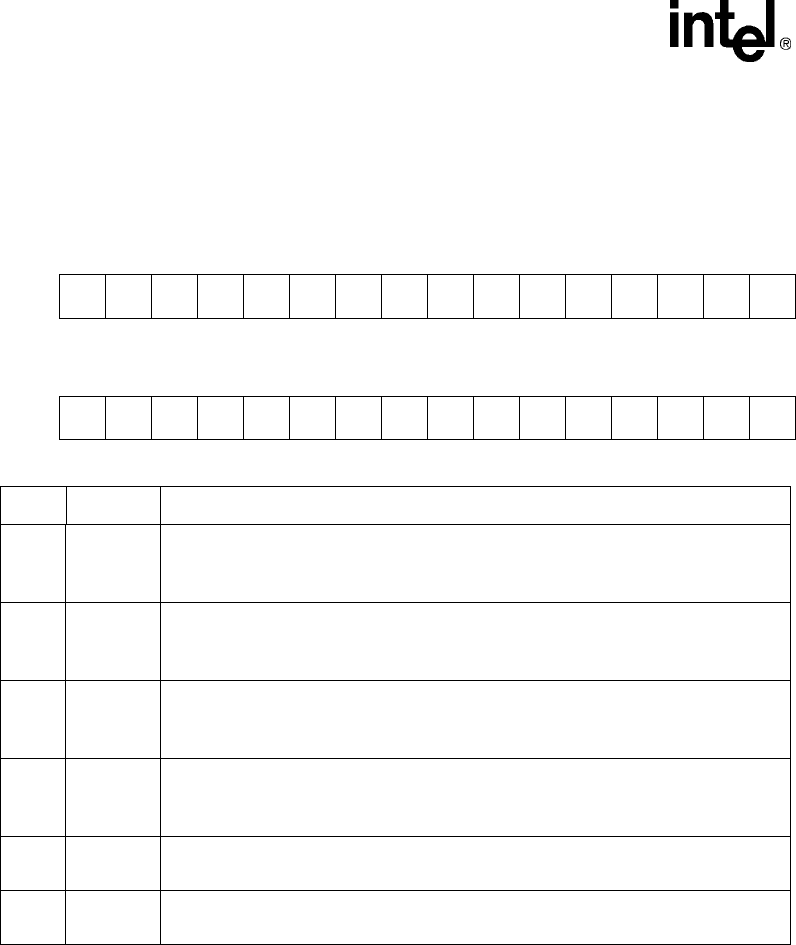

11.6.1.1 DMA Device Address Register (DDARn)

The DDARn is a 32-bit read/write register containing channel information regarding the target

device. Writes to this register are blocked if the RUN bit in the DCSRn is one. The following figure

shows the format for this register; question marks indicate that the values are unknown at reset.

.

1

“Partial” means that certain bits in the address are assumed to be zero. The DA<31:8> field is constructed as follows:

DA<31:28> = Device port address 31:28.

Device port address 27:22 is assumed to be zero.

DA<27:8> = Device port address 21:2.

Device port address 1:0 is assumed to be zero.

Bit31302928272625242322212019181716

Read

DA

31

DA

30

DA

29

DA

28

DA

27

DA

26

DA

25

DA

24

DA

23

DA

22

DA

21

DA

20

DA

19

DA

18

DA

17

DA

16

Reset0000????????????

-

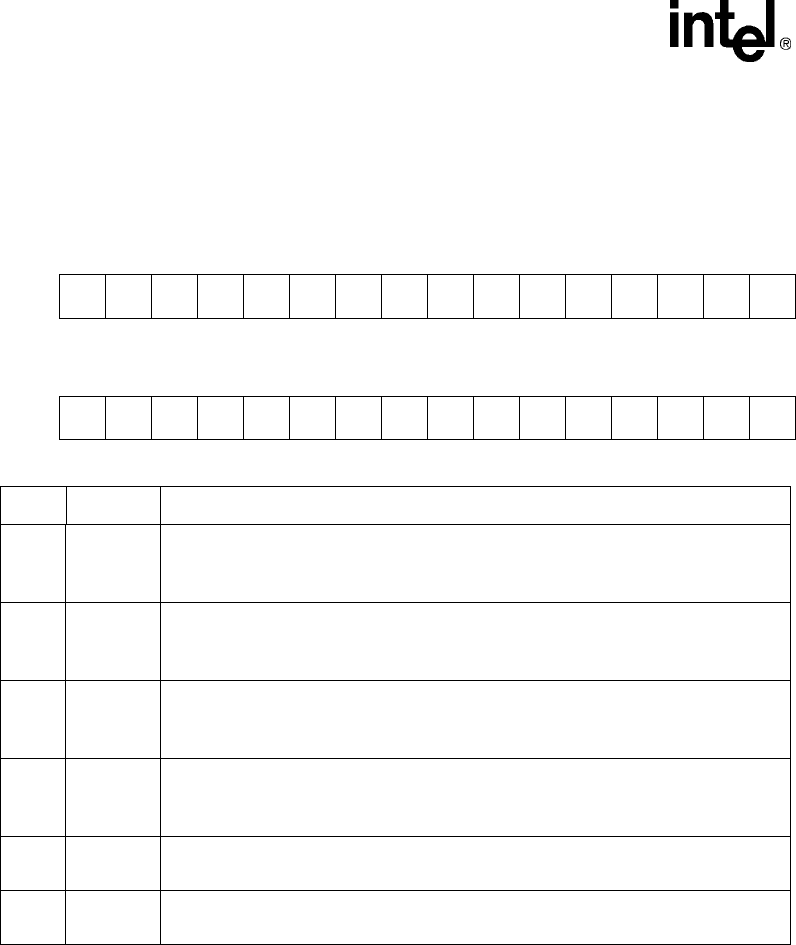

Bit1514131211109876543210

Read

DA

15

DA

14

DA

13

DA

12

DA

11

DA

10

DA

9

DA

8

DS

3

DS

2

DS

1

DS

0

DW BS E RW

Reset????????????????

Bit Name Description

0 RW Device data transfer direction (read/write).

0 = Transfer is a write (memory to device).

1 = Transfer is a read (device to memory).

1 E Device endianess.

0 = Byte ordering is little endian.

1 = Byte ordering is big endian.

2 BS Device burst size.

0 = Four datums per burst.

1 = Eight datums per burst.

3 DW Device datum width.

0 = Datum size is one byte.

1 = Datum size is one half-word.

7..4 DS<3:0> Device select.

This field is programmed to point to the desired device.

31..8 DA<31:8>

Device address field.

This field is a partial address of the data port of the device currently being serviced.

1