SA-1100 Developer’s Manual 10-17

Memory and PCMCIA Control Module

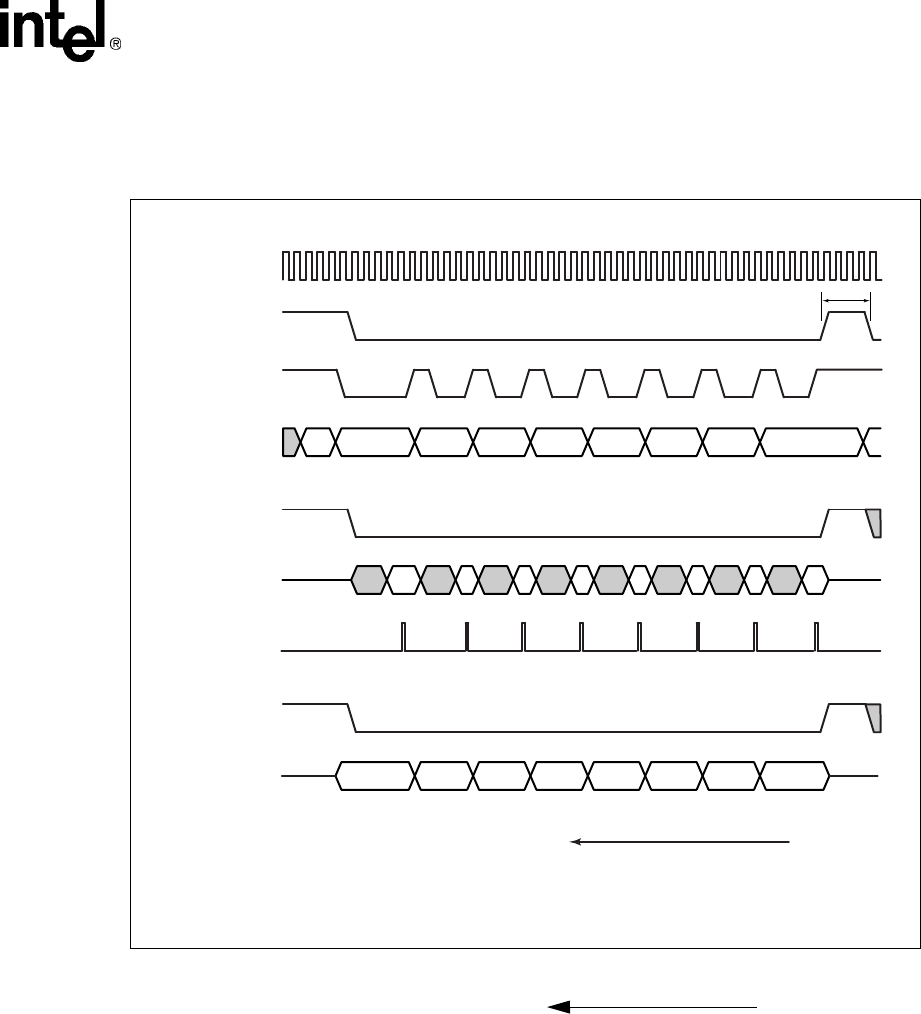

Figure 10-4 shows the rate of the shift registers during DRAM nCAS timing for burst-of-eight

transactions.

Figure 10-4. DRAM Burst-of-Eight Transactions

A4778-01

Memory Clock

ADDR

Input Data

Latch Input Data (internal):

Reads:

TRP

nRAS

nOE

Writes:

Write Data

nWE

nCAS

COL

D0

D1 D2 D3 D4 D5 D6 D7

COL+4 COL+8

COL+12 COL+16 COL+20 COL+24

COL+28

D0 D1 D2 D3 D4 D5 D6 D7

ROW

Contents of DRAM register fields:

MDCAS1 = 11 0001 1000 1100 (binary) MDCAS0 = 0110 0011 0001 1000 1100 0110 0000 0111 (binary)

firstlast

time

MDCNFG:TRP = 4 MDCNFG:CDB2 = 1 TDL = 00

Contents of DRAM register fields:

MDCNFG:TRP=4

MDCAS0= 0110 0011 0001 1000 1100 0110 0000 0111(binary)

MDCAS1=11 0001 1000 1100(binary)

MDCNFG:CDB2=1

TDL=00

time

first

last