SA-1100 Developer’s Manual 11-167

Peripheral Control Module

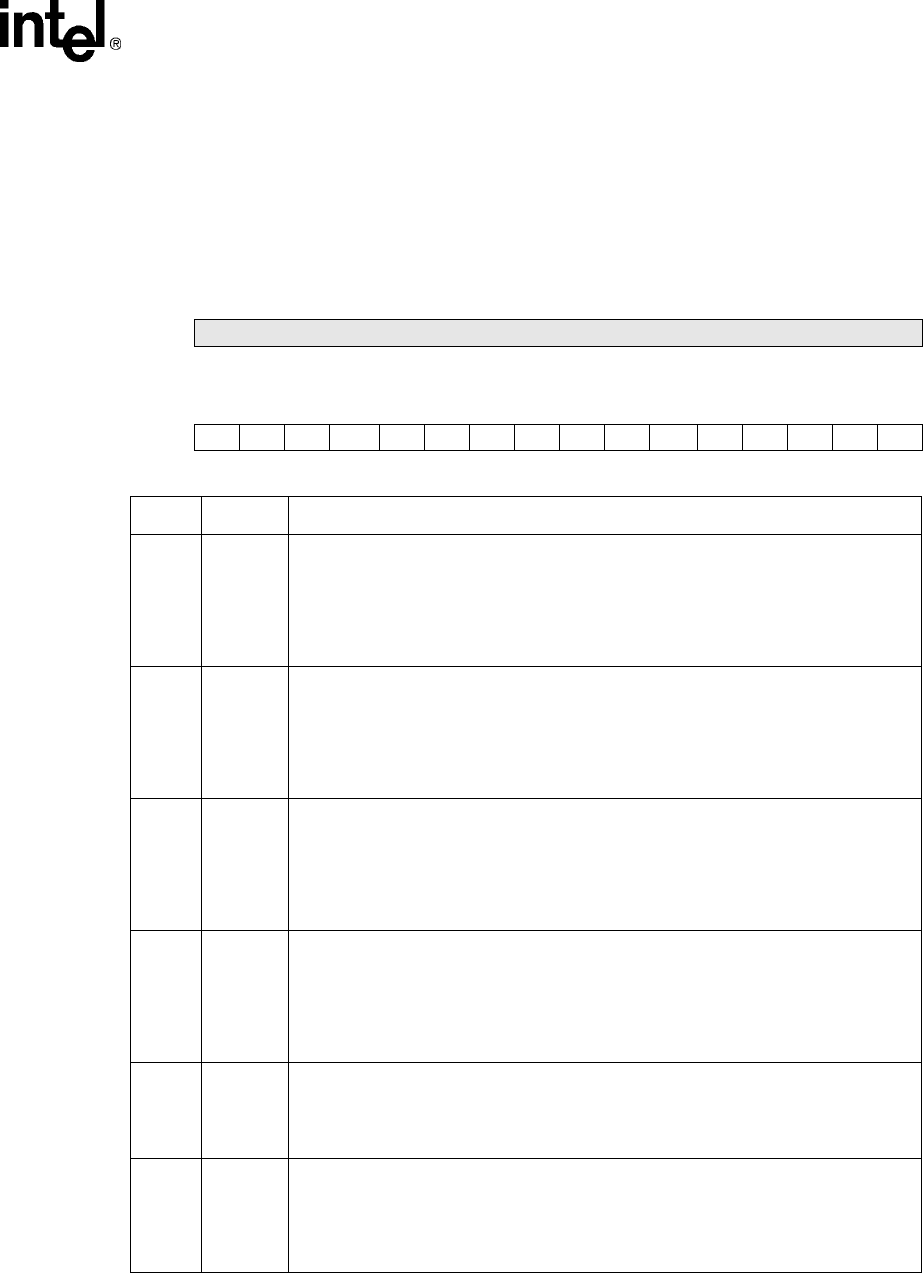

The following table shows the bit locations corresponding to the status and flag bits within the

MCP status register. MCSR contains a collection of read/write, read-only, interruptible, and

noninterruptible bits (refer to the bit descriptions above). Writes to read-only bits have no effect.

The user must clear set status bits before enabling the MCP. Note that writes to reserved bits are

ignored and reads return zeros; question marks indicate that the values are unknown at reset.

Address: 0h 8006 0018 MCP Status Register: MCSR

Read/Write &

Read-Only

Bit 31302928272625242322212019181716

Reserved

Reset0000000000000000

Bit1514131211109876543210

TCE ACE CRC CWC TNE TNF ANE ANF TRO TTU ARO ATU TRS TTS ARS ATS

Reset00000101????0000

Bit Name Description

0 ATS Audio transmit FIFO service request flag (read-only).

0 – Audio transmit FIFO is more than half-full (five or more entries filled) or MCP

disabled.

1 – Audio transmit FIFO is half-full or less (four or fewer entries filled) and MCP

operation is enabled, DMA service request signalled, interrupt request signalled if not

masked (if ATE=1).

1ARS

Audio receive FIFO service request (read-only).

0 – Audio receive FIFO is less than half-full (three or fewer entries filled) or MCP

disabled.

1 – Audio receive FIFO is half-full or more (four or more entries filled) and MCP

operation is enabled, DMA service request signalled, interrupt request signalled if not

masked (if ARE=1).

2 TTS Telecom transmit FIFO service request flag (read-only).

0 – Telecom transmit FIFO is more than half-full (five or more entries filled) or MCP

disabled.

1 – Telecom transmit FIFO is half-full or less (four or fewer entries filled) and MCP

operation is enabled, DMA service request signalled, interrupt request signalled if not

masked (if TTE=1).

3TRS

Telecom receive FIFO service request (read-only).

0 – Telecom receive FIFO is less than half full (three or fewer entries filled) or MCP

disabled.

1 – Telecom receive FIFO is half full or more (four or more entries filled) and MCP

operation is enabled, DMA service request signalled, interrupt request signalled if not

masked (if TRE=1).

4ATU

Audio transmit FIFO underrun.

0 – Audio transmit FIFO has not experienced an underrun.

1 – Audio transmit logic attempted to fetch data from transmit FIFO while it was empty

request interrupt.

5ARO

Audio receive FIFO overrun.

0 – Audio receive FIFO has not experienced an overrun.

1 – Audio receive logic attempted to place data into receive FIFO while it was full,

request

interrupt.