SA-1100 Developer’s Manual 6-3

Caches, Write Buffer, and Read Buffer

memory-management page table. For this reason, in order to use the Dcaches, the MMU must be

enabled. The two functions may be enabled simultaneously with a single write to the control

register.

Note: The Dcaches operate with virtual addresses, so care must be taken to ensure that their contents

remain consistent with the virtual-to-physical mappings performed by the memory-management

unit. If the memory mappings are changed, the validity of the Dcaches must be ensured.

6.2.1 Cacheable Bit – C

The cacheable bit determines whether, on load misses, the data being read should be placed in one

of the two data caches. Cache hits are not affected by the cacheable bit; if a data access hits in the

cache, the data is assumed to be valid and the load or store is performed. Typically, main memory is

marked as cacheable to improve system performance and I/O space as noncacheable to stop the

data from being stored in SA-1100’s cache. For example, if the processor is polling a hardware flag

in I/O space, it is important that the processor is forced to read data from the external peripheral,

and not a copy of initial data held in the cache.

6.2.1.1 Cacheable Reads – C = 1

A linefetch of 8 words will be performed and it will be placed in a cache bank with a round-robin

replacement algorithm.

6.2.1.2 Noncacheable Reads – C = 0

An external memory access will be performed and the cache will not be written.

6.2.2 Bufferable Bit – B

The bufferable bit does not affect writes that hit the Dcaches. If a store hits in the Dcaches, the store

is assumed to be bufferable. Write-backs of dirty lines are treated as bufferable writes. See the

Section 6.3, “Write Buffer (WB)” on page 6-5 for more information on the B bit.

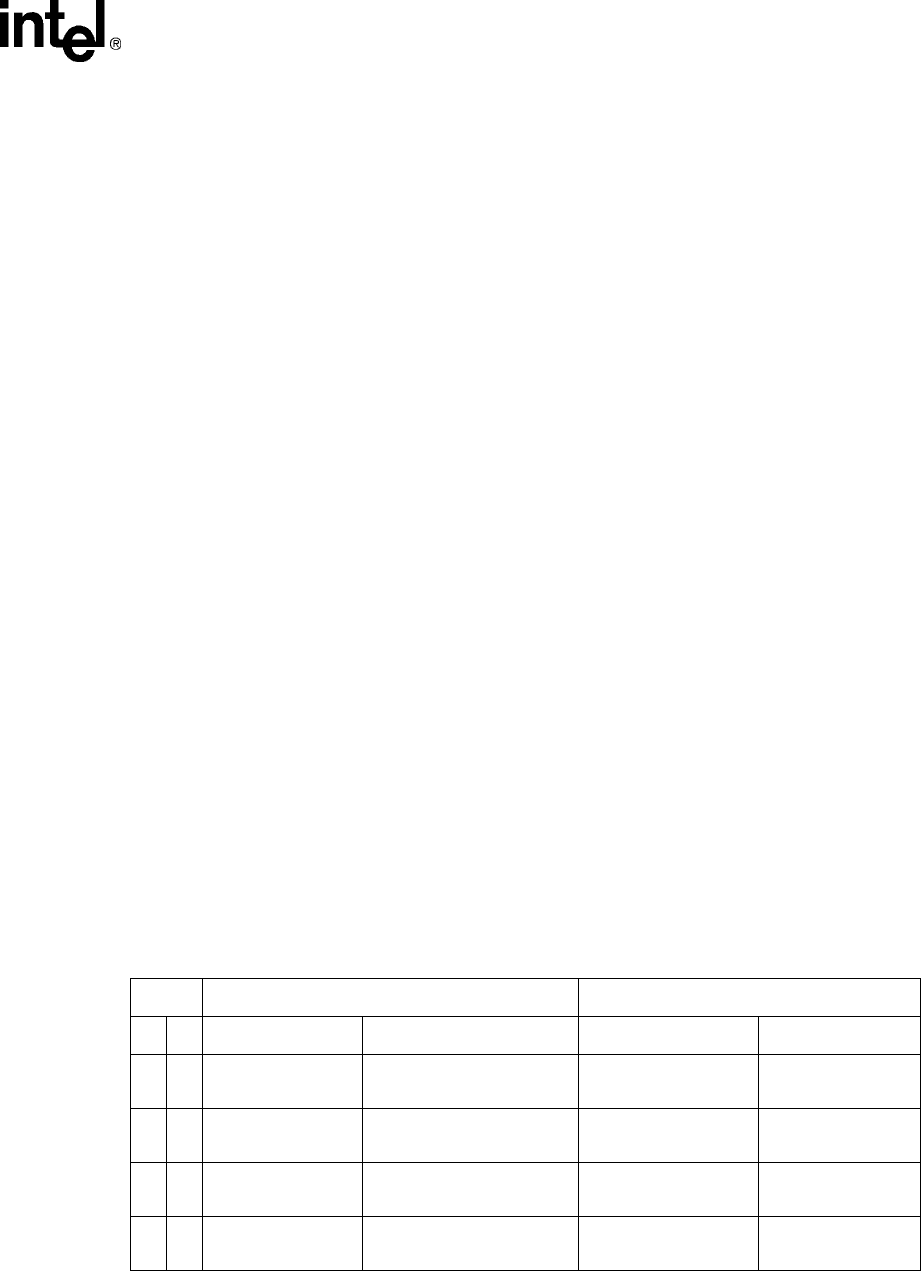

Table 6-1 summarizes the effects of the B and C bits on the Dcaches.

Table 6-1. Effects of the Cacheable and Bufferable Bits on the Data Caches

Load Store

BC

Cache Hit Cache Miss Cache Hit Cache Miss

0 0 Deliver cache data. Load from memory.

– No allocate.

Store to either cache.

– Mark line dirty.

Store to memory.

– No allocate.

0 1 Deliver cache data. Allocate to minicache. Store to either cache.

– Mark line dirty.

Store to memory.

– No allocate.

1 0 Deliver cache data. Load from memory.

– No allocate.

Store to either cache.

– Mark line dirty.

Store to memory.

– No allocate.

1 1 Deliver cache data. Allocate to main data cache. Store to either cache.

– Mark line dirty.

Store to memory.

– No allocate.