8-2 SA-1100

Developer’s Manual

Clocks

8.2 Core Clock Configuration Register

The core clock frequency is configured by software through the core clock configuration field

(CCF<4:0>) in the power manager phase-locked loop (PLL) configuration register (PPCR). This

field should be programmed during the boot sequence for the desired full-speed operation.

nRESET clears the field by selecting the lowest frequency operation.

See Section 9.5, “Power Manager” on page 9-26 for the physical address used to access this

register.

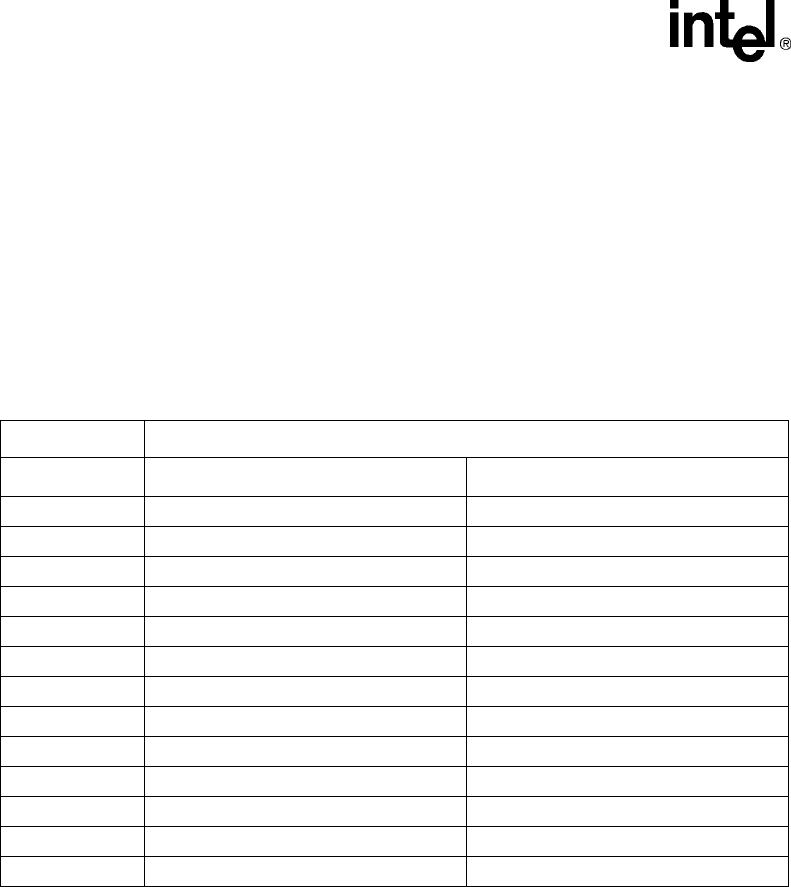

Table 8-1 shows the core clock frequency as a function of the CCF setting.

8.2.1 Restrictions on Changing the Core Clock Configuration

When the CPU writes to the PPCR, the core clock PLL and the 48-MHz PLL are stopped for a

period of time to allow the core clock PLL to relock to the new frequency. When these PLLs are

stopped, the core clock and all clocks derived from that clock are stopped. When this happens,

certain units within the SA-1100 (the LCD controller, all serial controllers, the DMA controller,

and the OS timer) will experience an interruption in operation for approximately 150 microseconds

after the PPCR is written.

Because of these restrictions, it is recommended that the user not change the PPCR except

immediately following a hard reset or immediately following wake-up from sleep mode. The LCD

controller, all serial controllers (except the UDC), the DMA controller, and the OS timer are

already disabled and are not affected by an interruption in their clock stream. In addition to these

restrictions, the PPCR must be written prior to enabling clock switching. Note that the 32.768-kHz

clock is not affected by any change in the PPCR and units using this clock (power management,

RTC) do not see any interruption in service during the 150 microsecond period.

Table 8-1. Core Clock Configurations

CCF<4:0> Core Clock Frequency in MHz

3.6864-MHz Crystal Oscillator 3.5795-MHz Crystal Oscillator

00000 59.0 57.3

00001 73.7 71.6

00010 88.5 85.9

00011 103.2 100.2

00100 118.0 114.5

00101 132.7 128.9

00110 147.5 143.2

00111 162.2 157.5

01000 176.9 171.8

01001 191.7 186.1

01010 206.4 200.5

01011 221.2 214.8

01100– 11111 Not supported. —