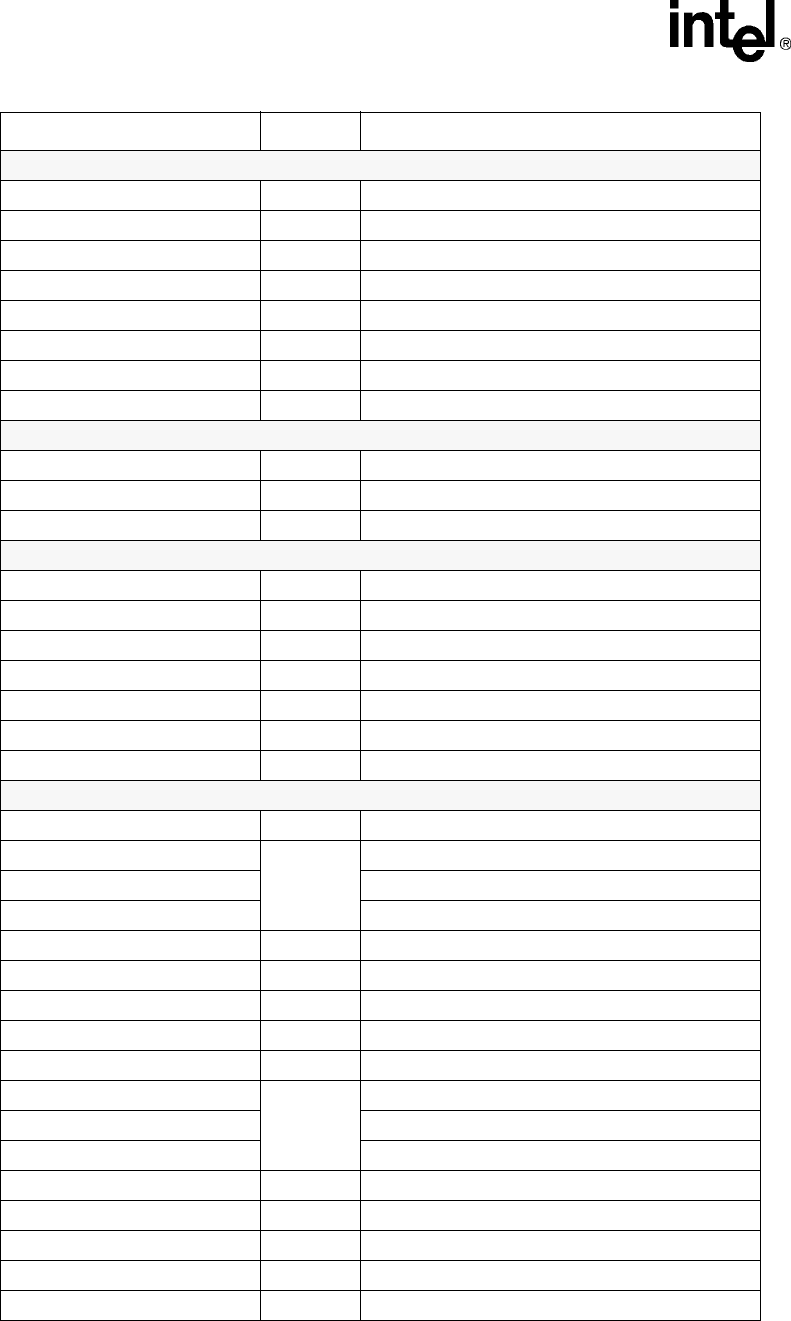

A-2 SA-1100

Developer’s Manual

Register Summary

Power Manager Registers

0h 9002 0000 PMCR Power manager control register.

0h 9002 0004 PSSR Power manager sleep status register.

0h 9002 0008 PSPR Power manager scratchpad register.

0h 9002 000C PWER Power manager wakeup enable register.

0h 9002 0010 PCFR Power manager configuration register.

0h 9002 0014 PPCR Power manager PLL configuration register.

0h 9002 0018 PGSR Power manager GPIO sleep state register.

0h 9002 001C POSR Power manager oscillator status register.

Reset Controller Registers

0h 9003 0000 RSRR Reset controller software reset register.

0h 9003 0004 RCSR Reset controller status register.

0h 9003 0008 TUCR Reserved for test.

Memory Controller Registers

0xA000 0000 MDCNFG DRAM configuration register.

0xA000 0004 MDCAS0 DRAM CAS waveform shift register 0.

0xA000 0008 MDCAS1 DRAM CAS waveform shift register 1.

0xA000 000C MDCAS2 DRAM CAS waveform shift register 2.

0xA000 0010 MSC0 Static memory control register 0.

0xA000 0014 MSC1 Static memory control register 1.

0xA000 0018 MECR Expansion bus configuration register.

DMA Controller Registers

0h B000 0000 DDAR0 DMA device address register.

0h B000 0004

DCSR0

DMA control/status register 0 – write ones to set.

0h B000 0008 Write ones to clear.

0h B000 000C Read only.

0h B000 0010 DBSA0 DMA buffer A start address 0.

0h B000 0014 DBTA0 DMA buffer A transfer count 0.

0h B000 0018 DBSB0 DMA buffer B start address 0.

0h B000 001C DBTB0 DMA buffer B transfer count 0.

0h B000 0020 DDAR1 DMA device address register 1.

0h B000 0024

DCSR1

DMA control/status register 1 – write ones to set.

0h B000 0028 Write ones to clear.

0h B000 002C Read only.

0h B000 0030 DBSA1 DMA buffer A start address 1.

0h B000 0034 DBTA1 DMA buffer A transfer count 1.

0h B000 0038 DBSB1 DMA buffer B start address 1.

0h B000 003C DBTB1 DMA buffer B transfer count 1.

0h B000 0040 DDAR2 DMA device address register 2.

Physical Address Symbol Register Name