SA-1100 Developer’s Manual 2-3

Functional Description

2.2 Inputs/Outputs

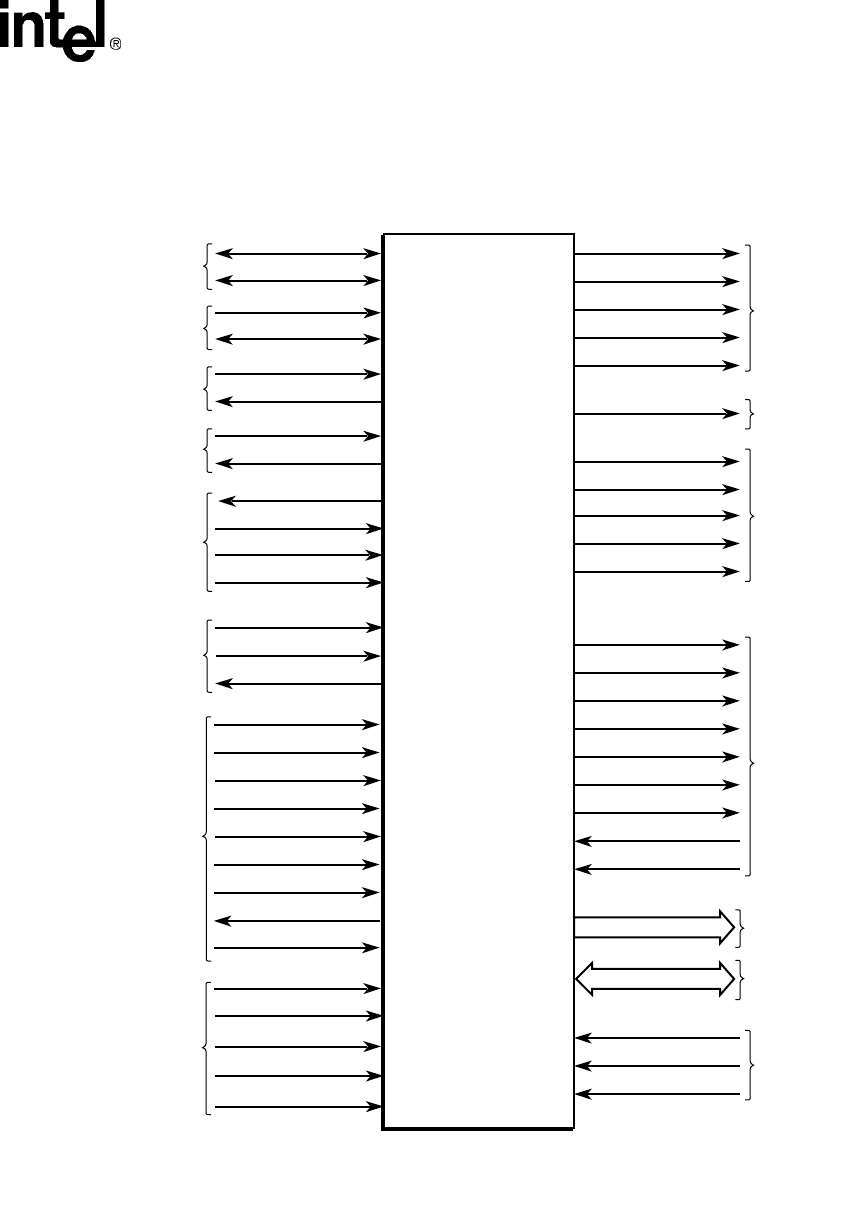

Figure 2-2. SA-1100 Functional Diagram

A6975-01

Intel

®

StrongARM

®*

SA-1100

[208-pins]

L_DD(7:0)

L_FCLK

L_LCLK

L_PCLK

L_BIAS

GP(27:0)

TXD _2

RXD _2

TXD_1

RXD _1

UDC+

UDC-

nCAS(3:0)

nRAS/(3:0)

nOE

nWE

nCS(3:0)

nPOE

nPWE

nPIOR

nPIOW

nPCE<2:1>

PSKTSEL

nPREG

nPWAIT

nIOIS16

Supply

Data Bus

VDD

VDDX

VSS/VSSX

PCMCIA

Bus

Signals

TCK_BYP

TESTCLK

PEXTAL

PXTAL

TEXTAL

TXTAL

nRESET

nRESET_OUT

ROM_SEL

Clocks, Reset

and Test

Memory

Control

Address

Bus

Serial

Channel 0

(USB)

Serial

Channel 1

(SDLC)

Serial

Channel 2

(IrDA)

TXD _3

RXD _3

Serial

Channel 3

(UART)

RXD _C

TXD _C

SFRM _C

SCLK _C

Serial

Channel 4

(CODEC)

TDI

TCK

TMS

nTRST

TDO

JTAG

BATT_FAULT

PWR_EN

VDD_FAULT

Power

Management

GPIO

Ports

LCD

Control

D<31:0>

A<25:0>

* StrongARM is a registered trademark of ARM Limited.