SA-1100 Developer’s Manual 11-157

Peripheral Control Module

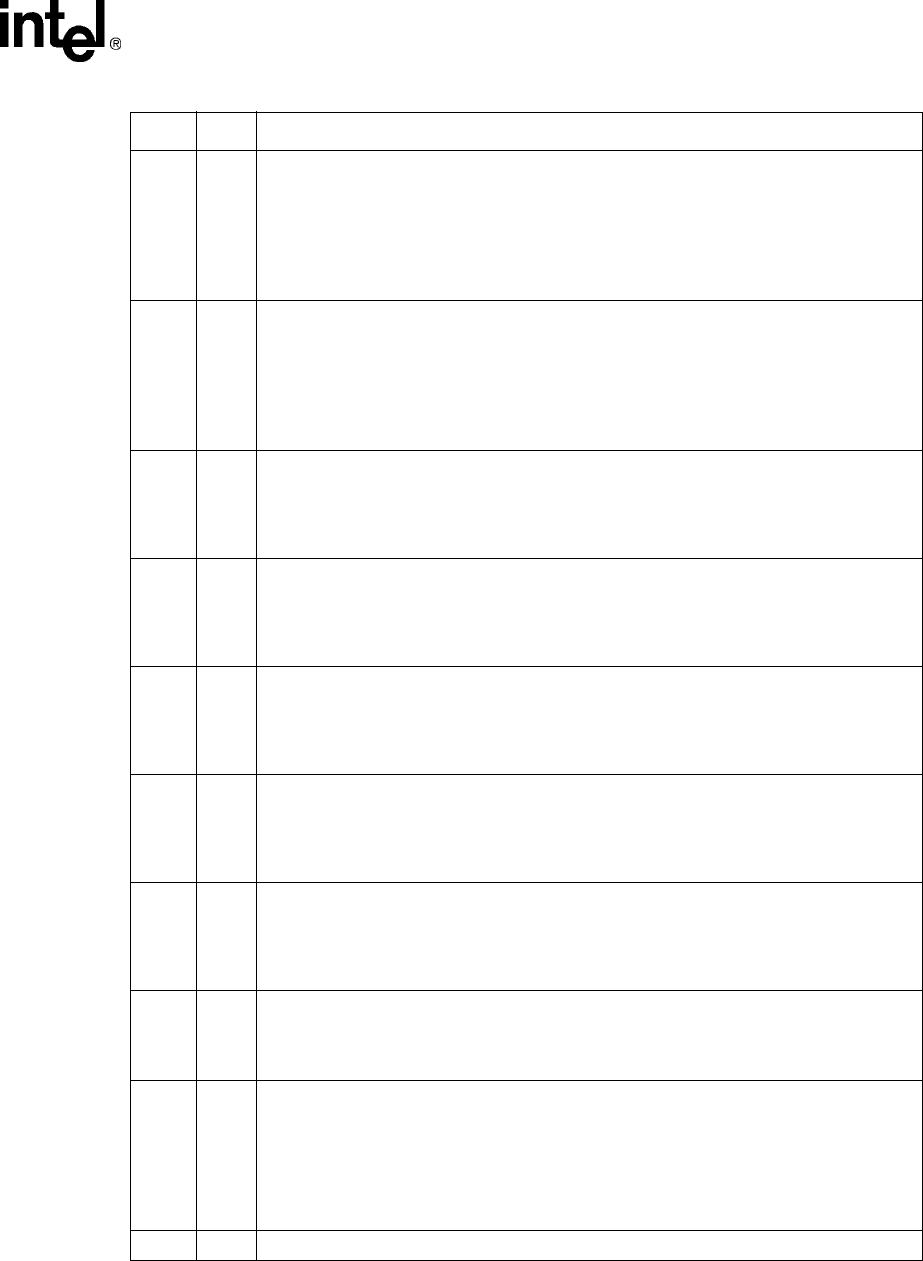

16 MCE Multimedia communications port enable.

0 – MCP operation disabled, control of the TXD4, RXD4, SCLK, and SFRM pins given to the

PPC to be used as general-purpose I/O pins.

1 – MCP operation enabled.

Note that the MCP has precedence over the SSP, if MCE=1; SSE is ignored unless the SPR

bit is set within the PPC, which allows the SSP to use GPIO pins while the MCP uses serial

port 4’s pin for transmission.

17 ECS

External clock select.

0 – on-chip clock used to produce the frame rate as further programmed by the CFS control

bit in MCCR1. It is also used to clock the audio and telecom sample rate counters.

1 – Clock input using GPIO pin 21 to select a frame rate that is an exact multiple of the

desired audio/telecom sample rate.

Frame Rate = Input Clock Freq /(ECP x 32).

Sample Rate = Input Clock Freq /(ECP x 32 x ASD or TSD).

18 ADM

A/D data sampling mode.

0 – Audio and telecom receive data is stored to their respective FIFOs whenever their receive

data valid bits are valid.

1– Audio and telecom receive data is stored when the receive data valid bit is set the first time,

and from that point on whenever the MCP’s audio and telecom sample rate counters time out.

19 TTE

Telecom transmit FIFO interrupt enable.

0 – Telecom transmit FIFO half-full or less condition does not generate an interrupt (TTS bit

ignored).

1 – Telecom transmit FIFO half-full or less condition generates an interrupt (state of TTS

sent to interrupt controller).

20 TRE

Telecom receive FIFO interrupt enable.

0 – Telecom receive FIFO one- to two-thirds full or more condition does not generate an

interrupt (TRS bit ignored).

1 – Telecom receive FIFO one- to two-thirds full or more condition generates an interrupt

(state of TRS sent to interrupt controller).

21 ATE

Audio transmit FIFO interrupt enable.

0 – Audio transmit FIFO half-full or less condition does not generate an interrupt (ATS bit

ignored).

1 – Audio transmit FIFO half-full or less condition generates an interrupt (state of ATS sent to

interrupt controller).

22 ARE

Audio receive FIFO interrupt enable.

0 – Audio receive FIFO one- to two-thirds full or more condition does not generate an

interrupt (ARS bit ignored).

1 – Audio receive FIFO one- to two-thirds full or more condition generates an interrupt (state

of ARS sent to interrupt controller).

23 LBM

Loopback mode.

0 – Normal serial port operation enabled.

1 – Output of serial shifter is connected to input of serial shifter internally and control of

TXD4, RXD4, SCLK, and SFRM pins is given to the PPC unit.

25..24 ECP

External clock prescaler.

00 – Clock input using GPIO pin 21 is divided by one before being used to drive the frame rate.

00 – Clock input using GPIO pin 21 is divided by two before being used to drive the frame rate.

00 – Clock input using GPIO pin 21 is divided by three before being used to drive the frame rate.

00 – Clock input using GPIO pin 21 is divided by four before being used to drive the frame rate.

Note: ECP is used only when ECS=1. Also, the maximum clock frequency allowed to drive

the frame rate after ECS has divided down the input clock is 12 MHz.

31.. 26 —

Reserved.

Bit Name Description