SA-1100 Developer’s Manual 5-1

Coprocessors

5

The operation and configuration of the Intel

®

StrongARM

®

SA-1100 Microprocessor (SA-1100) is

controlled with coprocessor instructions, configuration pins, and memory-management page

tables. The coprocessor 15 instructions manipulate on-chip registers that control the configuration

of the cache, write buffer, MMU, read buffer, breakpoints, and other configuration options.

Note: The gray areas in the register and translation diagrams are reserved and should be programmed 0

for future compatibility.

5.1 Internal Coprocessor Instructions

The on-chip cache, MMU, write buffer, and read buffers are controlled using MRC instructions and

MCR instructions. These operations to coprocessor 15 are allowed only in nonuser modes except

when read-buffer operations are explicitly enabled. The undefined instruction trap is taken if

accesses are attempted in user mode. Figure 5-1 shows the format of internal coprocessor

instructions MRC and MCR.

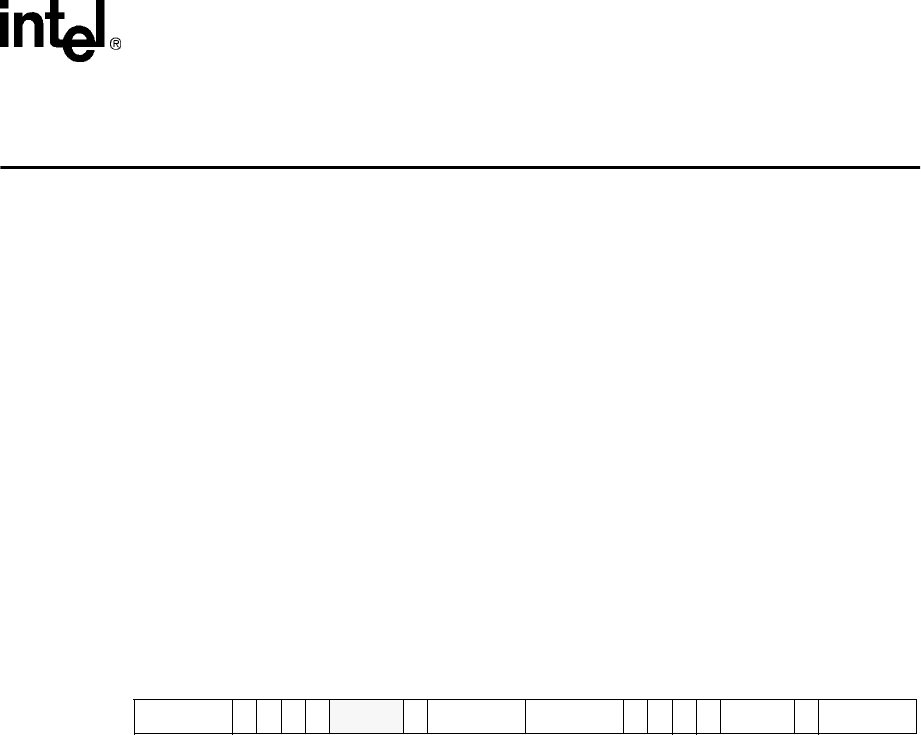

Figure 5-1. Format of Internal Coprocessor Instructions MRC and MCR

Cond ARM™

condition codes

n 1 MRC register read

0 MCR register write

CRn SA-1100 register

Rd ARM register

OPC_2 Function bits for some MRC/MCR instructions

CRm Function bits for some MRC/MCR instructions

1110 n 1111 1

034578111215161920212324272831

Cond

CRn Rd

OPC_2 CRm