SA-1100 Developer’s Manual 11-43

Peripheral Control Module

11.7.8 DMA Channel 1 Base Address Register

DMA channel 1 base address register (DBAR1) is a 32-bit register that is used to specify the base

address of the off-chip frame buffer for DMA channel 1. The base address pointer register can be

both read and written. Addresses programmed in the base address register must be aligned on

quadword boundaries; the least significant four bits (DBAR1<3:0>) must always be written with

zeros. The user must initialize the base address register before enabling the LCD, and can also

write a new value to it while the LCD is enabled to allow a new frame buffer to be used for the next

frame. The user can change the state of DBAR1 while the LCD controller is active just after the

base address update (BAU) status bit is set with the LCD’s status register, which generates an

interrupt request. This status bit indicates that the value in the base address pointer has transferred

to the current address pointer register and that it is safe to write a new base address value. DMA

channel 1 is used to transfer frame buffer data from off-chip memory to the LCD’s input FIFO and

the palette RAM for single-panel mode, and for the top half of the screen in dual-panel mode. For

dual-panel operation, the user must perform the following sequence in order: disable the LCD

(LEN=0), program dual panel mode (SDS= 0

→ 1), write the upper panel DMA base address,

write the lower panel DMA base address, enable the LCD

(LEN= 0 → 1). Note that DBAR1 is not

reset and must be initialized before enabling the LCD; question marks indicate that the values are

unknown at reset.

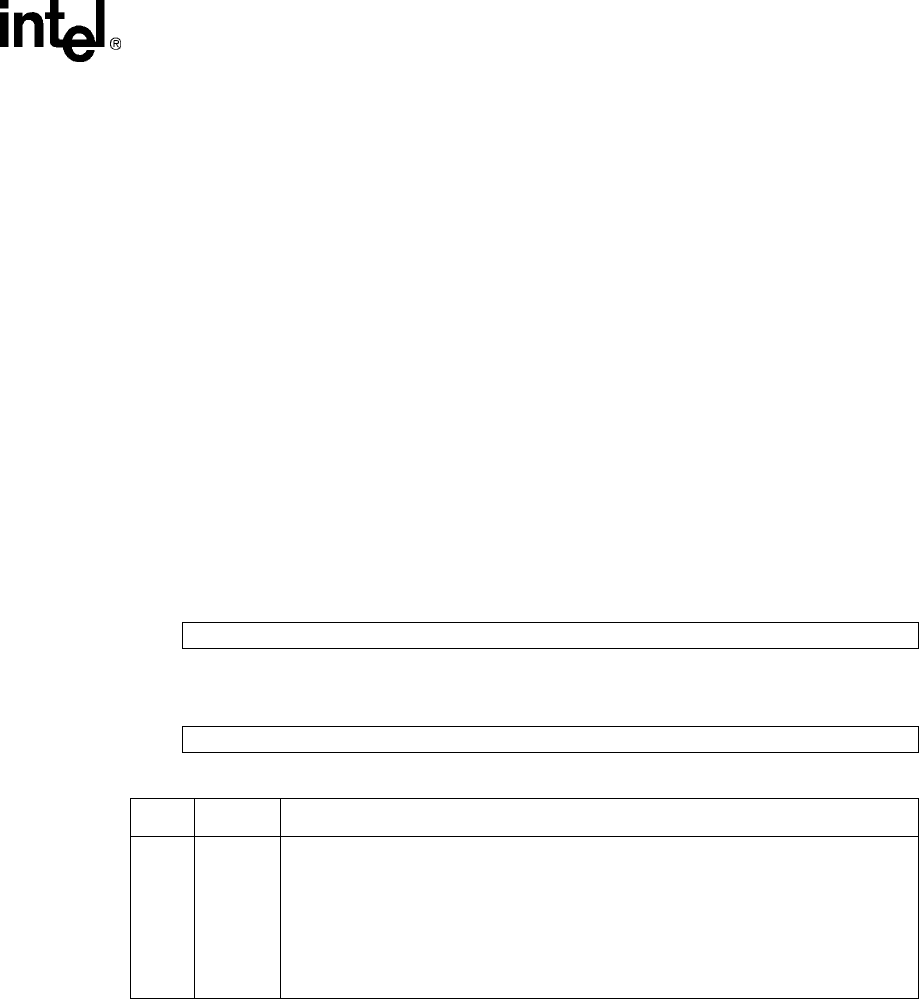

Address: 0h B010 0010 DBAR1: DMA Channel 1 Base Address Register Read/Write

Bit31302928272625242322212019181716

DMA Channel 1 Base Address Pointer

Reset????????????????

--

Bit1514131211109876543210

DMA Channel 1 Base Address Pointer

Reset????????????????

Bit Name Description

31..0 DBAR1

DMA channel 1 base address pointer.

Used to specify the base address of the frame buffer within off-chip memory. Value in

DBAR1 is transferred to current address pointer register 1 when LCD is first enabled

(LEN= 0 → 1) and when the current address pointer value equals the end-of-frame

buffer. DBAR1 should be written only when the LCD is disabled or immediately after an

interrupt is generated by the setting of the base address update (BAU) status bit. The

base address must be on a quadword boundary; the user must always write bits 0

through 3 to zero.