11-162 SA-1100

Developer’s Manual

Peripheral Control Module

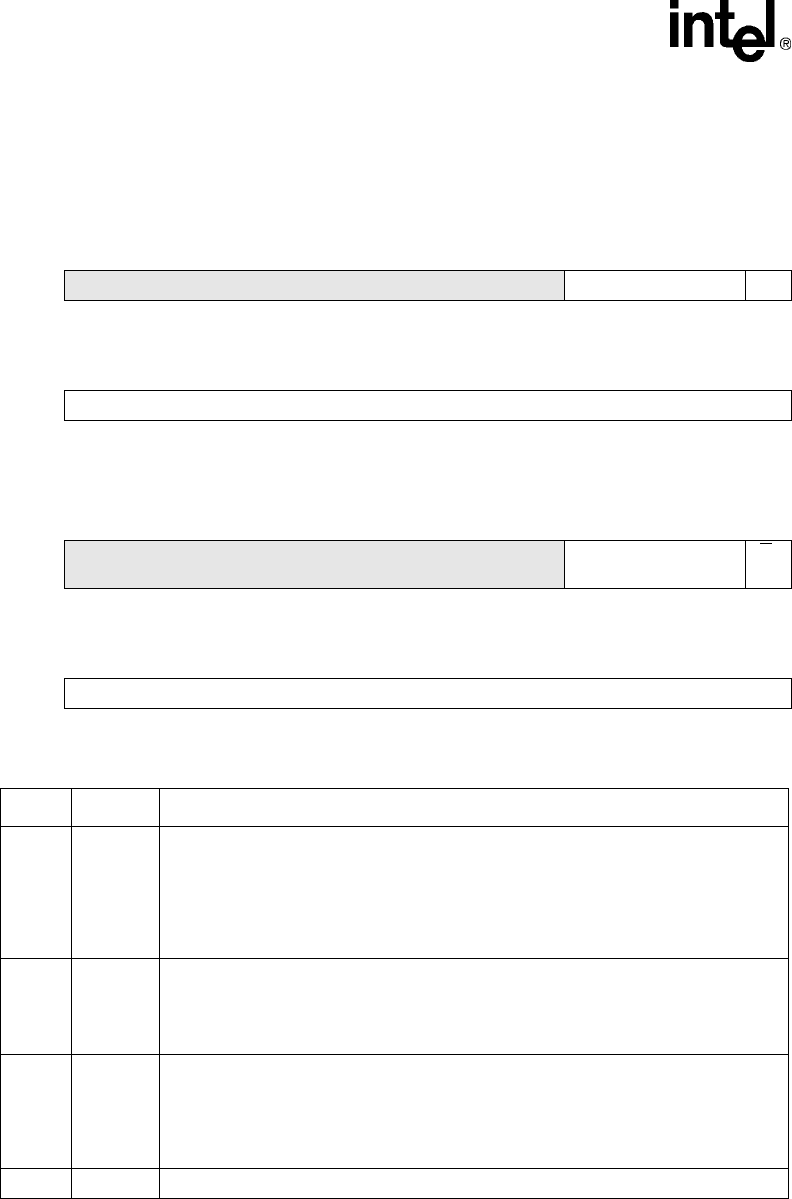

The following table shows the location of MCP data register 2. Note that the reset state of all

MCDR2 bits is unknown (indicated by question marks), writes to reserved bits are ignored, and

reads return zeros.

.

Address: 0h 8006 0010 MCP Data Register 2: MCDR2 Read/Write

Bit 31302928272625242322212019181716

Reserved Reg Address R/W 0

Reset00000000000?????

Bit1514131211109876543210

Data Value Returned by a Codec Register Read or Write

Reset????????????????

Read Access

Bit 31302928272625242322212019181716

Reserved Reg Address R/W

R

/

W

Reset00000000000?????

Bit1514131211109876543210

Data Value to be Written to the Addressed Codec Register

Reset????????????????

Write Access

Bit Name Description

15..0 Codec

Register

Read/

Write

Data

Codec register read/write data.

Read – If a codec write was last performed, contains data of previous register access;

next frame contains the data that was written. If a codec read was last performed,

contains data from the read register.

Write – Used to specify what data to write to the addressed register, ignored for a codec

register read.

16 R/W

Read/write.

Read – Returns a zero.

Write – Used to control whether the addressed register is read or written (write = 1,

read = 0).

20..17 Codec

Register

Read/

Write

Address

Codec register read/write address.

Read – If a codec write was last performed, contains address of previous register

access; next frame contains the address of the write. If a codec read was last

performed, contains address of the register read.

Write – Used to address a register to perform a read or write.

31.. 21 —

Reserved.