SA-1100 Developer’s Manual 11-53

Peripheral Control Module

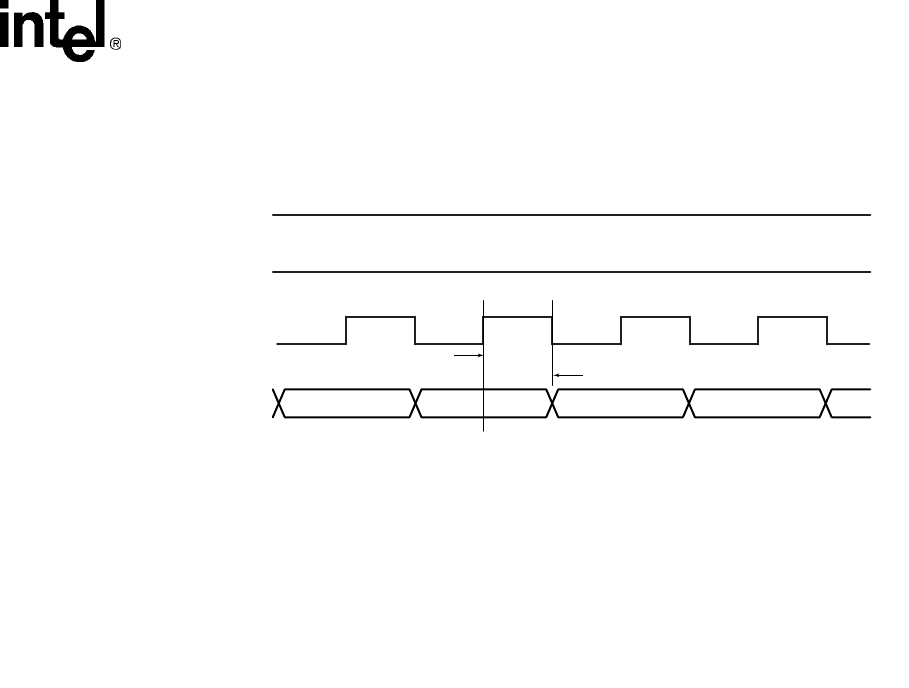

Figure 11-12. Passive Mode Pixel Clock and Data Pin Timing

A4792-01

L_FCLK

L_LCLK

L_PCLK

LDD[3:0]*

*DPD = 0

Notes:

PCP - Pixel clock polarity:

0 - Pixels sampled from data pins on rising edge of pixel clock.

1 - Pixels sampled from data pins on falling edge of pixel clock.

DPD - Dual pixel data mode:

0 - 4 data pins are used in single-panel monochrome mode.

1 - 8 data pins are used in single-panel monochrome mode.

Pixels 0 through 3

PCP = 0

Data Pins Change

Data Pins Sampled

by the Display

Pixels 4 through 7 Pixels 8 through 11 Pixels 12 through 15