11-106 SA-1100

Developer’s Manual

Peripheral Control Module

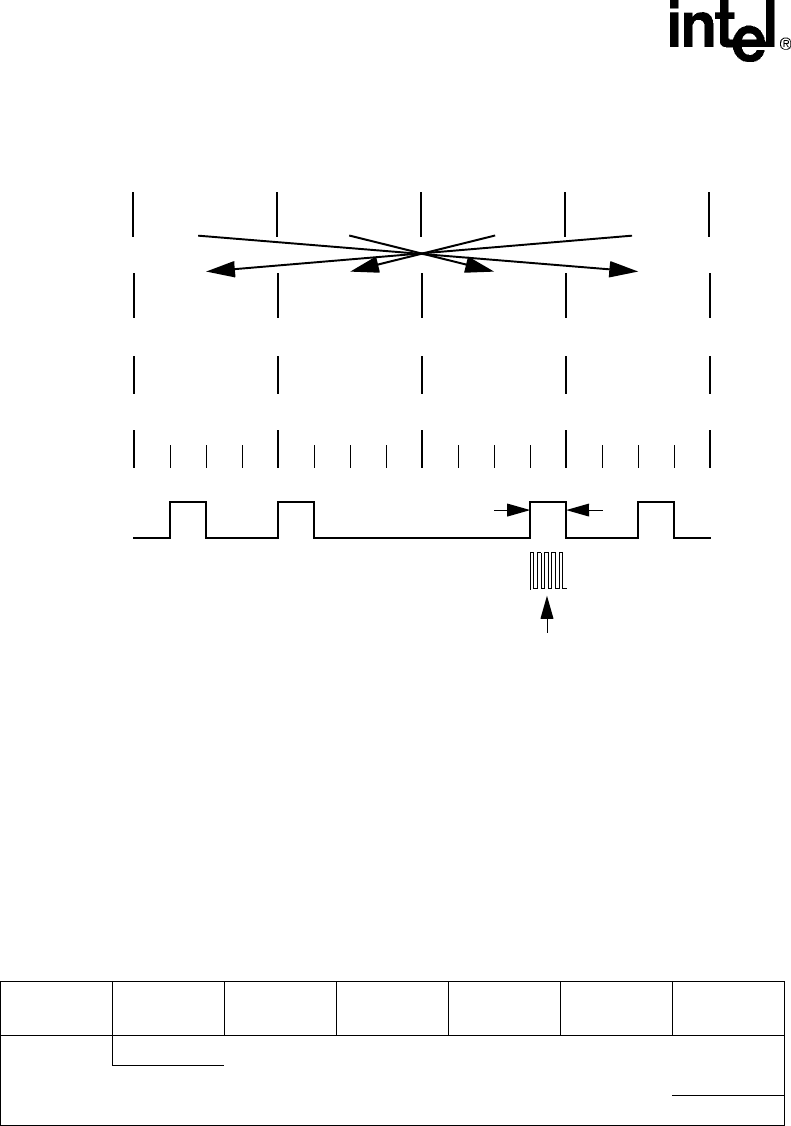

11.10.2.2 HSSP Frame Format

When the 4-Mbps transmission rate is used, the high-speed serial/parallel (HSSP) interface within

the ICP is used along with the 4PPM bit encoding. The high-speed frame format shown in

Figure 11-28 is similar to serial port 1’s SDLC format with several minor modifications: the

start/stop flags and CRC are twice as long, and instead of one start flag, a preamble and start flag of

differing lengths are used.

Figure 11-28. High-Speed Serial Frame Format for IrDA Transmission (4.0 Mbps)

The preamble, start, and stop flags are a mixture of chips that contain either 0, 1, or 2 pulses within

the four timeslots. Chips with 0 and 2 pulses are used to construct flags because they represent invalid

data bit pairings (one pulse required per chip to represent one of four bit pairs). The preamble

contains 16 repeated transmissions of the four chips: 1000 0000 1010 1000; the start flag contains one

transmission of eight chips: 0000 1100 0000 1100 0110 0000 0110 0000; and the stop flag contains

one transmission of eight chips: 0000 1100 0000 1100 0000 0110 0000 0110. The address, control,

data, and CRC-32 use the standard 4PPM chip encoding to represent 2 bits per chip.

Figure 11-27. 4PPM Modulation Example

4PPM

Data

Reordered

Nibbles

01001110

125ns

Timeslots

1234123412341234

Chips

1

2

34

Receive data sample counter frequency = 6X pulse width; each timeslot sampled on third clock.

Original

Byte Order

10110001

Nibble 3Nibble 2Nibble 1Nibble 0

Nibble 0Nibble 1Nibble 2Nibble 3

64 chips 8 chips

4 chips

(8 bits)

4 chips

(8 bits)

8180 chips

max

(2045 bytes)

16 chips

(32 bits)

8 chips

Preamble Start Flag Address

Control

(optional)

Data CRC-32 Stop Flag

Start Flag |0000|1100|0000|1100|0110|0000|0110|0000|

|0000|1100|0000|1100|0000|0110|0000|0110| Stop Flag

Preamble |1000|0000|1010|1000|... repeated 16 times