SA-1100 Developer’s Manual 11-115

Peripheral Control Module

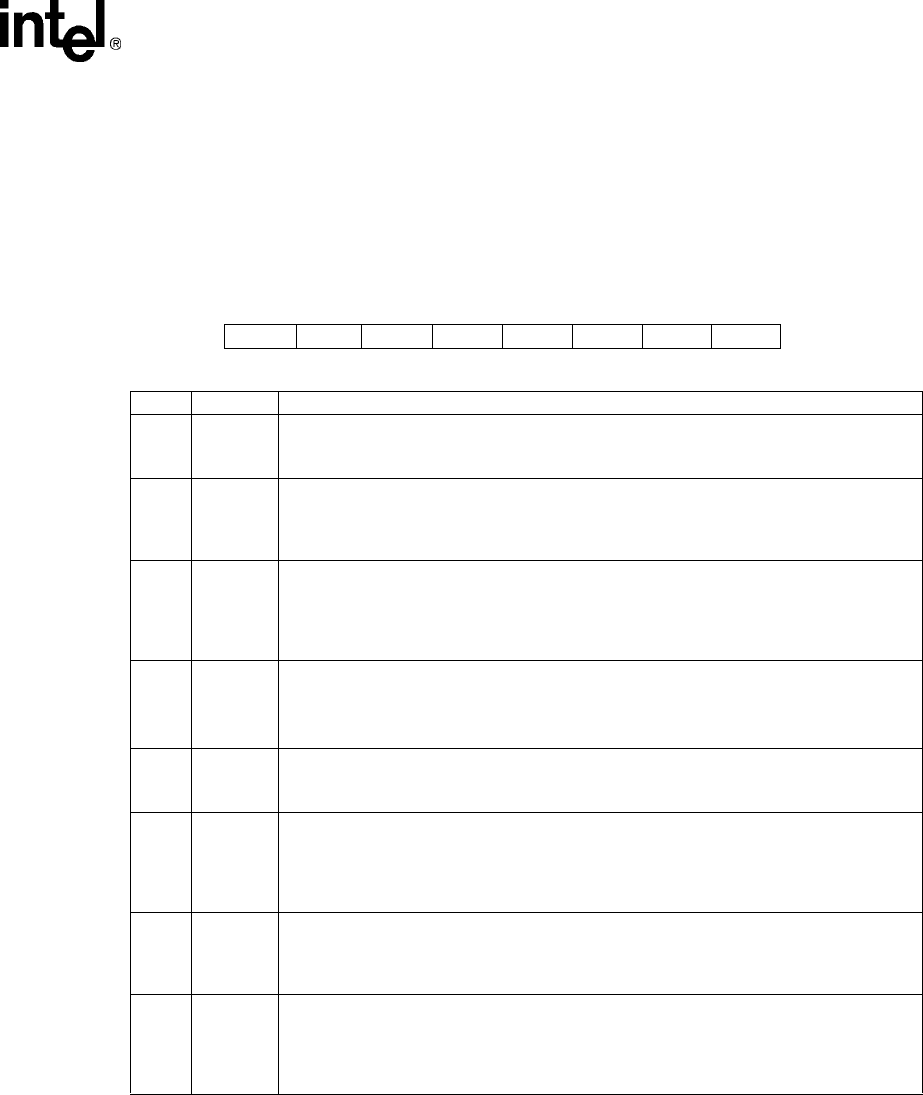

The following table shows the location of the bits within HSSP control register 0. RXE and TXE

are the only control bits that are reset to a known state to ensure the HSSP is disabled following a

reset of the SA-1100. The reset state of all other control bits is unknown (indicated by question

marks) and must be initialized before enabling the HSSP. Note that the HSSP must be disabled

(RXE=TXE=0) when changing the state of bits 0 and 1, and bits 2 through 7 may be written while

the HSSP is enabled to allow various modes to be changed during active operation.

Address: 0h 8004 0060 HSCR0 Read/Write

Bit 7 6 5 4 3 2 1 0

AME TIM RIM RXE TXE TUS LBM ITR

Reset ? ? ? 0 0 ? ? ?

Bit Name Description

0ITR

IrDA transmission rate.

0 – 115.2 Kbps (selects HP-SIR modulation, enables the ICP’s UART engine).

1 – 4.0 Mbps (selects 4PPM modulation, enables the ICP’s HSSP engine).

1LBM

Loopback mode.

0 – Normal serial port operation enabled.

1 – Output of HSSP’s transmit serial shifter is connected to input of receive serial shifter

internally. Control of TXD2 and RXD2 pins is given to the PPC unit if ITR=1.

2TUS

Transmit FIFO underrun select.

0 – Transmit FIFO underrun causes CRC, stop flag, and SIP to be transmitted, and

masks transmit underrun interrupt generation (TUR ignored).

1 –Transmit FIFO underrun causes an abort to be transmitted, and generates an interrupt

(state of TUR sent to interrupt controller).

3TXE

Transmit enable.

0 – HSSP transmit logic disabled; control of the TXD2 pin is given to the PPC unit if ITR=1.

1 – HSSP transmit logic enabled if ITR=1.

Note: A SIP is transmitted immediately after the transmitter is enabled (TXE = 0 → 1).

4RXE

Receive enable.

0 – HSSP receive logic disabled; control of the RXD2 pin is given to the PPC unit if ITR =1.

1 – HSSP receive logic enabled if ITR=1.

5RIE

Receive FIFO interrupt enable.

0 – Receive FIFO two- or three-fifths full or more condition does not generate an

interrupt (RFS bit ignored).

1 – Receive FIFO two- or three-fifths full or more condition generates an interrupt (state

of RFS sent to interrupt controller).

6TIE

Transmit FIFO interrupt enable.

0 – Transmit FIFO half-full or less condition does not generate an interrupt (TFS bit ignored).

1 – Transmit FIFO half-full or less condition generates an interrupt (state of TFS sent to

interrupt controller).

7AME

Address match enable.

0 – Disable receiver address match function, store data from all incoming frames in

receive FIFO.

1 – Enable receiver address match function; do not FIFO data unless address

recognized or incoming address contains all ones (0hFF).