D-2 SA-1100

Developer’s Manual

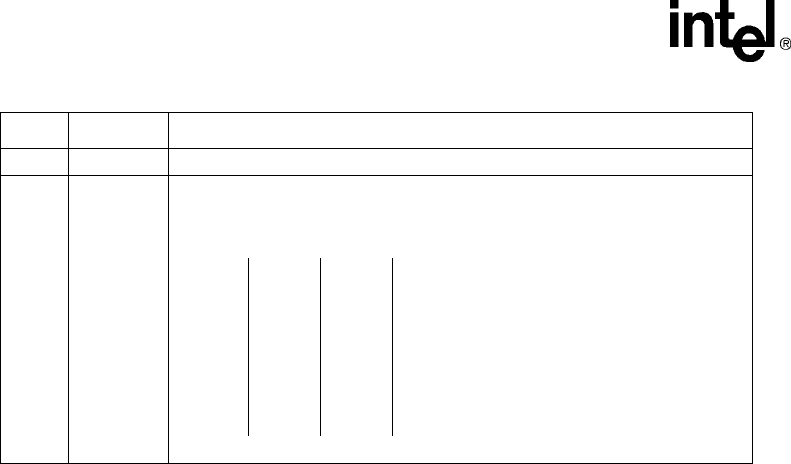

Internal Test

27..28 Reserved —

29..31 TSEL2-0 Test selects. Routes internal signals out onto GPIO<27> for observing internal

clock signals. To observe these clocks, set bit 27 to one in the GAFR and GPDR

registers and set the TSEL bits to the following settings to select which clock is

driven onto GP<27>:

TSEL2

0

0

0

0

1

1

1

1

TSEL1

0

0

1

1

0

0

1

1

TSEL0

0

1

0

1

0

1

0

1

GP<27>(alternate function)

32-kHz oscillator

3.6864-MHz oscillator

VDD ring oscillator/16

96-MHz PLL/4

32-kHz oscillator (also enable rclk on GP<26>

3.6864-MHz oscillator

Main PLL/16

VDDL ring oscillator/4

Bit Name Description