SA-1100 Developer’s Manual 11-11

Peripheral Control Module

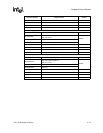

11.6.1.2 DMA Control/Status Register (DCSRn)

The DCSRn is a 32-bit read/write register that contains control and status bits for the channel. The

following figure shows the format for this register; question marks indicate that the values are

unknown at reset.

The RUN bit is the channel enable. It should be written to a one when the channel is ready for a

transfer. It can also be used to pause the channel in the middle of a transfer; when it is set to a one

again, the channel will resume from the current pointer value using the current active buffer. If the

RUN bit is cleared in the middle of a burst, the burst will complete before the channel is paused.

The DDAR may be written only when RUN is zero.

Bit31302928272625242322212019181716

Read Reserved

Reset00000000000000?00

--

Bit1514131211109876543210

Read Reserved BIU

STR

TB

DON

EB

STR

TA

DON

EA

ERR

OR

IE RUN

Reset????????????????

Bit Name Description

0RUN

Run bit.

This is a control bit and is set by the user to indicate that the device address register has

been loaded. No transfer will occur on this channel unless this bit is set. Clearing the RUN

bit on an active channel acts as a pause to that channel. Operation can then be resumed

by again setting the RUN bit.

1 IE Interrupt enable.

This bit enables interrupts to be passed onto the interrupt controller. An interrupt is the

“OR” of the DONEA, DONEB, and ERROR bits.

2 ERROR Transfer error bit.

ERROR is a status bit and is set to indicate that a memory error has occurred. It can generate

an interrupt if the IE bit is set. ERROR is cleared by software through setting the RUN bit.

3 DONEA Buffer A done.

This bit is a status bit and indicates that the transfer into or out of buffer A has completed.

It is cleared by writing a one to it or by setting the STRTA bit. DONEA can generate an

interrupt if IE is set.

4 STRTA Buffer A transfer start.

This bit is a control bit and is written by the user. It causes the buffer A transfer to begin.

This bit is functional only if the RUN bit is set.

5 DONEB This bit is a status bit and indicates that the transfer into or out of buffer B has completed.

It is cleared by writing a one to it or by setting the STRTB bit. DONEB can generate an

interrupt if IE is set.

6 STRTB Buffer B transfer start.

This bit is a control bit and is written by the processor. It causes the buffer B transfer to

begin. This bit is functional only if the RUN bit is set.

7 BIU Buffer in use.

BIU is a status bit and may be read to indicate which buffer (A or B) is active . This bit is

toggled by the DMA controller when DONEA or DONEB are set. This bit is cleared by all

reset sources (hard, sleep, watchdog, or software).

8..31 — Reserved.

These bits are reserved and read as zeros. Writes to this field have no effect.