11-48 SA-1100

Developer’s Manual

Peripheral Control Module

11.7.11.10 Output FIFO Underrun Lower Panel Status (OUL) (read/write,

maskable interrupt)

The output FIFO underrun lower panel status (OUL) bit is set when the lower panel’s output FIFO

is completely empty and the LCD’s data pin driver logic attempts to fetch data from the FIFO. It is

cleared by writing a one to the bit. This bit is used only in dual-panel mode (SDS=1). When this bit

is set, an interrupt request is made to the interrupt controller if it is unmasked (ERM=0).

11.7.11.11 Output FIFO Overrun Upper Panel Status (OOU) (read/write,

maskable interrupt)

The output FIFO overrun upper panel status (OOU) bit is set when the LCD’s dither logic attempts

to place data into the upper panel’s output FIFO after it has been completely filled. It is cleared by

writing a one to the bit. This bit is used in single-panel mode (SDS=0) and dual-panel mode

(SDS=1). When this bit is set, an interrupt request is made to the interrupt controller if it is

unmasked (ERM=0).

11.7.11.12 Output FIFO Underrun Upper Panel Status (OUU) (read/write,

maskable interrupt)

The output FIFO underrun upper panel status (OUU) bit is set when the upper panel’s output FIFO

is completely empty and the LCD’s data pin driver logic attempts to fetch data from the FIFO. It is

cleared by writing a one to the bit. This bit is used in single-panel mode (SDS=0) and dual-panel

mode (SDS=1). When this bit is set, an interrupt request is made to the interrupt controller if it is

unmasked (ERM=0).

The following table shows the location of the status and flag bits in LCSR. For reserved bits, writes

are ignored and reads return zero. Set status bits should be cleared by software before enabling

both the LCD controller and interrupt controller.

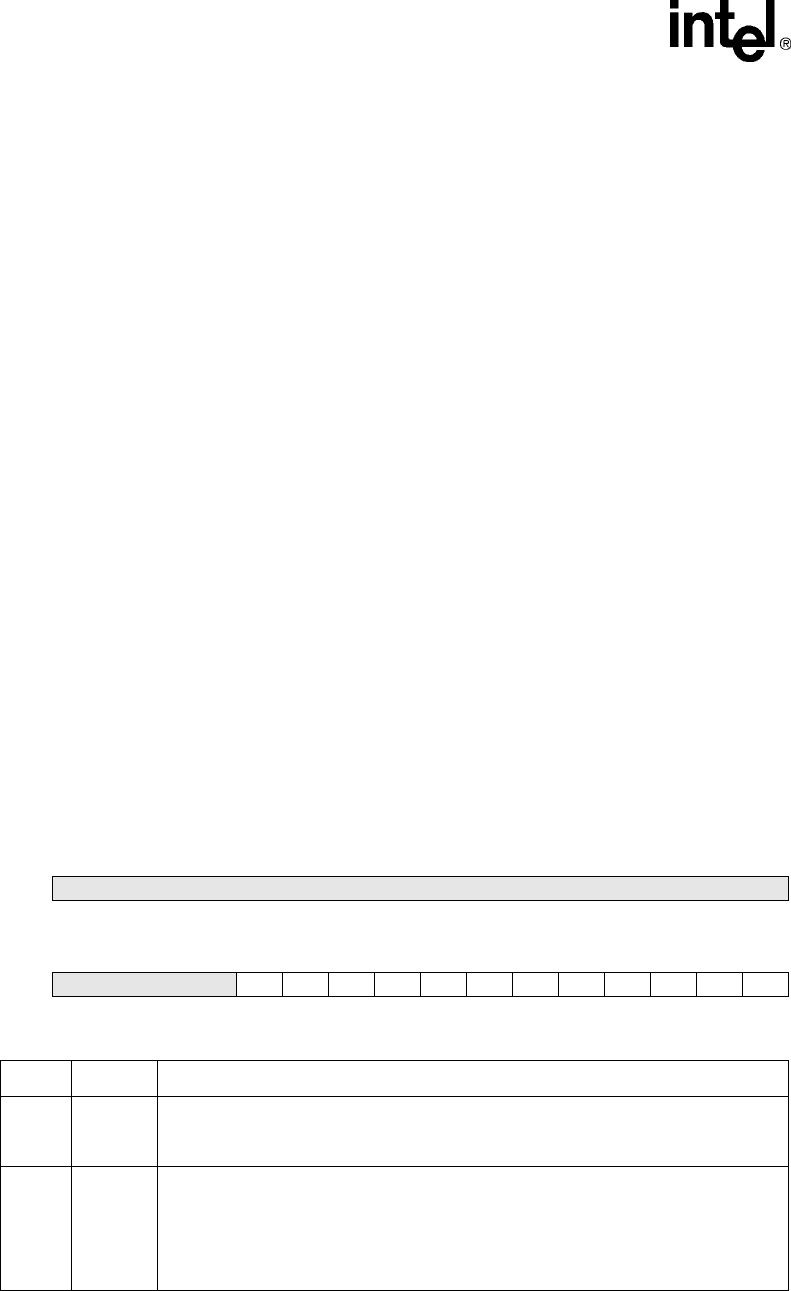

Address: 0h B010 0004 LCSR: LCD Status Register

Read/Write &

Read-Only

Bit31302928272625242322212019181716

Reserved

Reset0000000000000000

Bit1514131211109876543210

Reserved OUU OOU OUL OOL IUU IOU IUL IOL ABC BER BAU LFD

Reset0000000000000001

Bit Name Description

0 LDD

LCD disable done flag.

0 – LCD has not been disabled and the last active frame completed.

1 – LCD has been disabled and the last active frame has just completed.

1BAU

Base address update flag (read-only).

0 – Base address has been written and has not yet been transferred to the current

address register.

1 – Base address has been transferred to the current address register, triggered either

by enabling the LCD or when the current address pointer equals the end address value

calculated by the LCD.