11-12 SA-1100

Developer’s Manual

Peripheral Control Module

The IE bit is the interrupt enable for the channel. An interrupt is generated if the DONEA,

DONEB, or ERROR bits are set and the IE bit is set. The interrupt is negated when all of these

status bits are cleared.

The ERROR bit is set if the DMA controller is incorrectly programmed and points to reserved

memory space. No error is generated for references to nonexistent external memory. If enabled,

ERROR generates a channel interrupt.

The DONEA bit is a status bit set by the DMA controller to indicate that the transfer to or from

buffer A has completed. If enabled, DONEA causes a channel interrupt.

The STRTA bit is written by the user to start the channel transfer to or from buffer A. When

DONEA is set, STRTA is cleared. The immediate action resulting from setting STRTA is

dependent on the state of the BIU bit.

The DONEB bit is a status bit set by the DMA controller to indicate that the transfer to or from

buffer B has completed. If enabled, DONEB will cause a channel interrupt.

The STRTB bit is written by the user to start the channel transfer to or from buffer B. When

DONEB is set, STRTB is cleared. The immediate action resulting from setting STRTB is

dependent on the state of the BIU bit.

The BIU bit indicates the current buffer-in-use (A or B). If BIU is a zero, buffer A is in use. If BIU

is a one, buffer B is in use.The setting of DONEA or DONEB toggles the BIU bit. This bit is never

cleared except on reset (either hardware, software, or sleep). For this reason, the processor must

interrogate this bit before programming the channel for a new transfer. If both STRTA and STRTB

are set at the same time, the first buffer serviced depends on the state of BIU.

11.6.1.3 DMA Buffer A Start Address Register (DBSAn)

The DBSAn is a 32-bit read/write register that contains the starting memory address for buffer A.

This register may be written only when STRTA is zero.

11.6.1.4 DMA Buffer A Transfer Count Register (DBTAn)

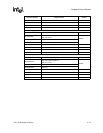

The DBTAn is a 32-bit read/write register that contains the current transfer count in bytes for buffer

A. This register may be written only when the STRTA bit for this channel is a zero. The following

figure shows the format of this register; question marks indicate that the values are unknown at reset.

.

Bit31302928272625242322212019181716

Read Reserved

Reset00000000000000?00

Bit1514131211109876543210

Read Reserved

TCA

12

TCA

11

TCA

10

TCA

9

TCA

8

TCA

7

TCA

6

TCA

5

TCA

4

TCA

3

TCA

2

TCA

1

TCA

0

Reset????????????????

Bit Name Description

0..12 TCA<12:0>

Transfer count (buffer A).

This field is a 13-bit value and contains the current transfer count (in bytes) for the transfer

to or from buffer A. The maximum value programmed via this transfer count is 8 Kbyte.

13..31 — Reserved. These bits are reserved and read as zeros. Writes to this field have no effect.