SA-1100 Developer’s Manual 4-1

Instruction Set

4

This section describes the instruction timing for the Intel

®

StrongARM

®

SA-1100 Microprocessor

(SA-1100).

4.1 Instruction Set

The SA-1100 implements the ARM

™

V4 architecture as defined in the ARM Architecture

Reference, 28-July-1995, with previously noted options and additions.

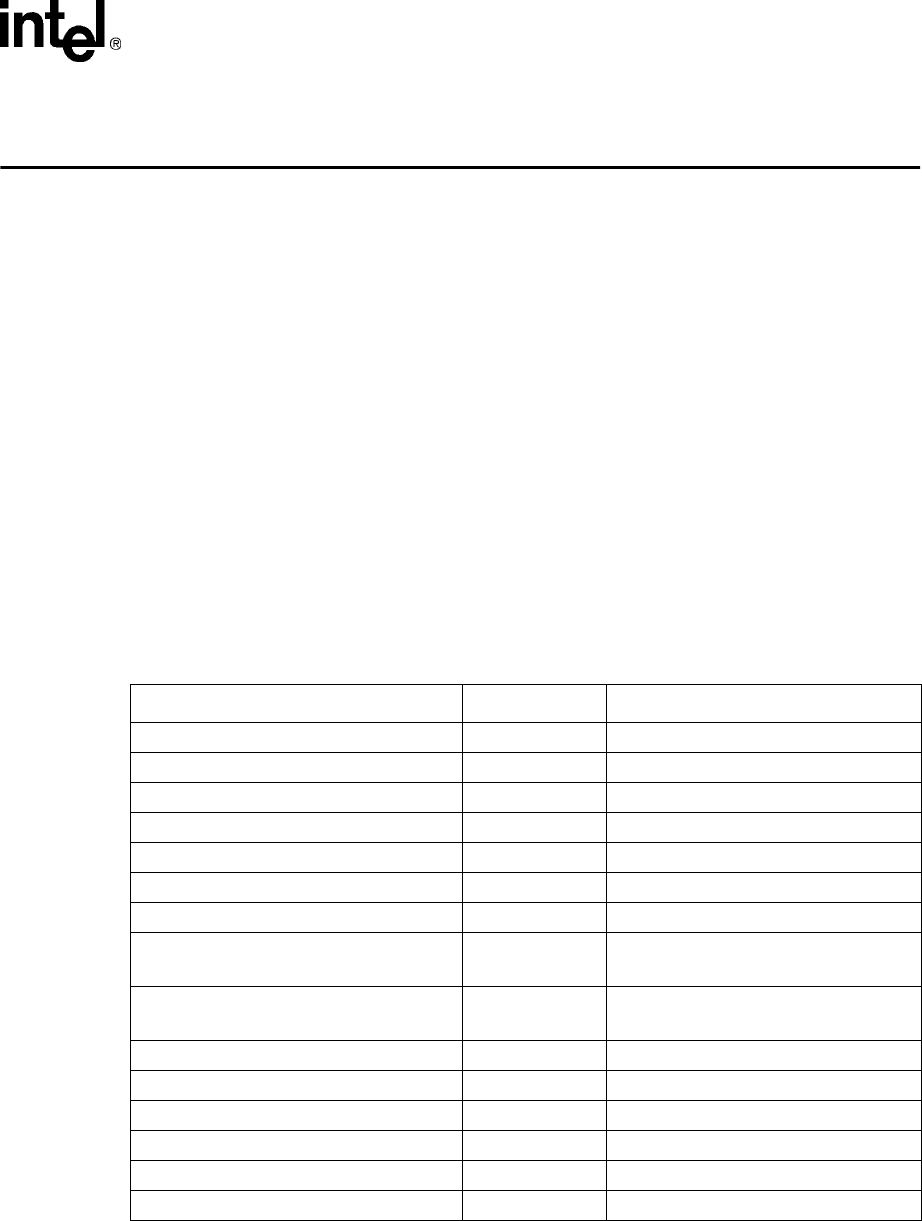

4.2 Instruction Timings

Table 4-1 lists the instruction timing for the SA-1100. The result delay is the number of cycles that

the next sequential instruction would stall if it used the result as an input. The issue cycles are the

number of cycles that this instruction takes to issue. For most instructions, the result delay is zero

and the issue cycles is one. For load and stores, the timing is for cache hits.

Table 4-1. Instruction Timings

Instruction Group Result Delay Issue Cycles

Data processing 0 1

Mul or Mul/Add giving 32-bit result 1..3 1

Mul or Mul/Add giving 64-bit result 1..3 2

Load single – write-back of base 0 1

Load single – load data zero extended 1 1

Load single – load data sign extended 2 1

Store single – write-back of base 0 1

Load multiple (delay for last register) 1

MAX

(2, number of registers loaded)

Store multiple – write-back of base 0

MAX

(2, number of registers loaded)

Branch or branch and link 0 1

MCR 2 1

MRC 1 1

MSR to control 0 3

MRS 0 1

Swap 2 2