SA-1100 Developer’s Manual 11-13

Peripheral Control Module

11.6.1.5 DMA Buffer B Start Address Register (DBSBn)

The DBSBn is a 32-bit read/write register that contains the starting memory address for buffer B.

This register may be written only while STRTB in the DCSR is zero.

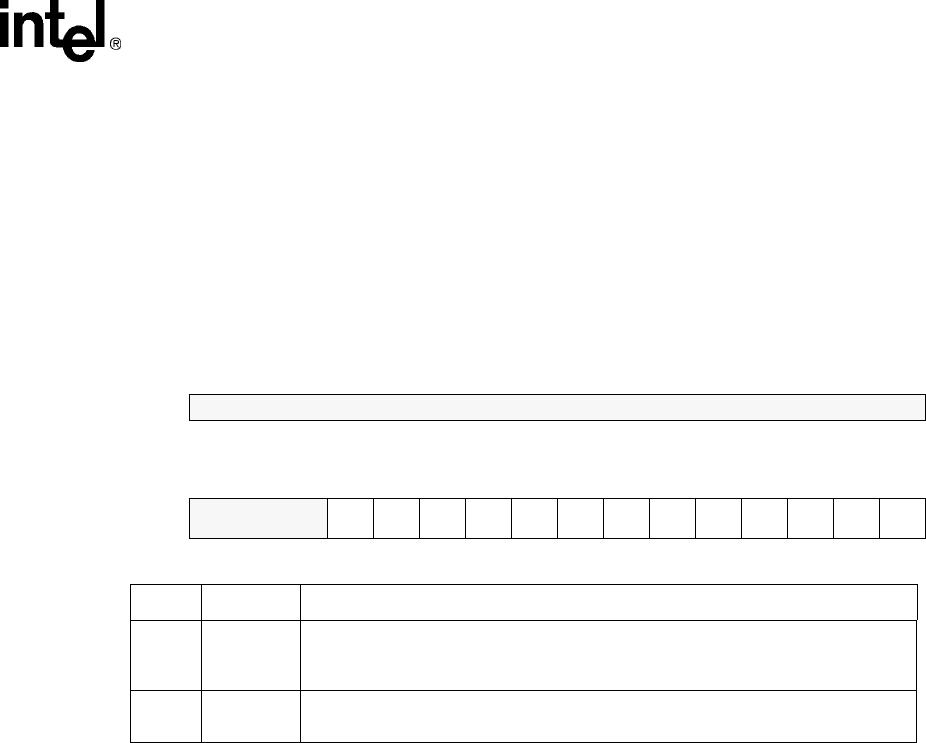

11.6.1.6 DMA Buffer B Transfer Count Register (DBTBn)

The DBTBn is a 32-bit read/write register that contains the current transfer count in bytes for buffer

B. This register may be written only when the STRTB bit for this channel is a zero. The following

figure shows the format of this register; question marks indicate that the values are unknown at reset.

11.6.2 DMA Operation

The DMA controller provides dynamic context switching between active channels on a demand

basis. A context switch may occur when a channel completes a command or when a particular burst

(portion of a transfer) has been completed. For example, if the FIFO in a particular transmit serial

controller is full and cannot accept more data, that channel may be switched out of the active

context in favor of another channel that is requesting service. An active channel may actually go

idle many times as the device is serviced. Channels are serviced in a fixed priority with channel 0

being the highest and channel 5 being the lowest.

Bit31302928272625242322212019181716

Read Reserved

Reset00000000000000?00

Bit1514131211109876543210

Read Reserved

TCB

12

TCB

11

TCB

10

TCB

9

TCB

8

TCB

7

STC

B6

TCB

5

TCB

4

TCB

3

TCB

2

TCB

1

TCB

0

Reset????????????????

Bit Name Description

0..12 TCB<12:0>

Transfer count (buffer B).

This field is a 13-bit value and contains the current transfer count (in bytes) for the transfer

to or from buffer B. The maximum value programmed via this transfer count is 8 Kbyte.

13..31 — Reserved.

These bits are reserved and read as zeros. Writes to this field have no effect.