9-42 SA-1100

Developer’s Manual

System Control Module

9.6.1 Reset Controller Registers

The reset controller contains two registers, the reset controller software reset register (RSRR) and

the reset controller reset status register (RCSR).

9.6.1.1 Reset Controller Software Reset Register (RSRR)

The reset controller software reset register has a software reset bit, which when set, causes a reset

of the SA-1100. The software reset bit (SWR) is located within the least significant bit of the

write-only reset controller software reset register (RSRR). Writing a one to this bit causes all

on-chip resources to reset but does not cause the PLL to go out of lock. The software reset bit is

self-resetting. It is automatically cleared to zero several system clock cycles after a one is written to

it. Writing zero to the software reset bit has no effect. Care should be taken to restrict access to this

register by programming MMU permissions. For reserved bits, writes have no effect. Reading this

register returns zeros.

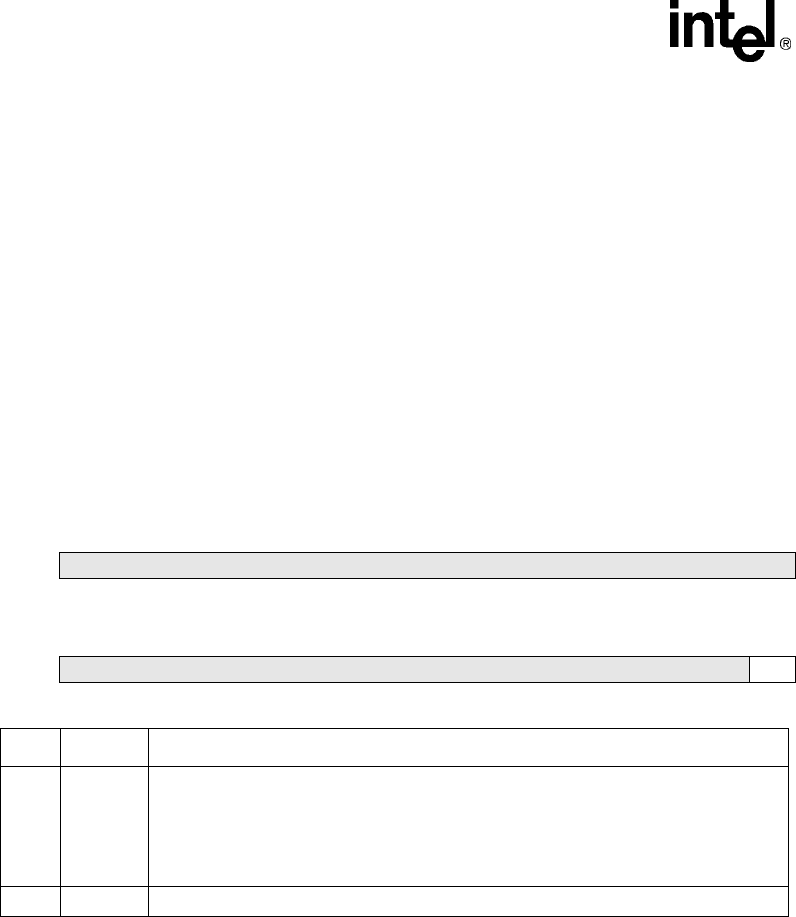

The following table shows the RSRR.

Bit31302928272625242322212019181716

Write Reserved

Reset0000000000000000

Bit1514131211109876543210

Write Reserved SWR

Reset0000000000000000

Bit Name Description

0SWR

Software reset.

0 – Do not invoke a software reset of the chip.

1 – Invoke a software reset of the chip.

Note: This bit is self-resetting, and is automatically cleared several system clock cycles

after it has been set.

31..1 — Reserved.