11-4 SA-1100

Developer’s Manual

Peripheral Control Module

11.3 Interrupts

Each peripheral unit interfaces to the interrupt controller within the system control module. The

interrupt controller contains a 32-bit interrupt pending register, which when read, informs the user

of all the units on the SA-1100 that are currently generating an unmasked interrupt. Once the user

determines which unit is causing the interrupt, the unit’s status registers can be read to determine

the exact cause of the interrupt. This mechanism provides a two-level approach to identify the

source of any interrupt from the hundreds of possible interrupt sources that exist on the SA-1100.

Each of the peripheral units generate either one or two interrupts that correspond to specific

interrupt pending bits within the interrupt controller. Serial ports 1 and 4 each contain two

independent serial engines. Although each peripheral uses only one set of pins for serial

communication, the user may choose to use both serial engines within serial ports 1 and 4 by

assigning one of the two protocols to communicate off-chip by taking control of GPIO pins.

Because the two engines within serial ports 1 and 4 can operate at the same time, these two units

are assigned two separate interrupt request numbers within the interrupt controller’s pending

register. Table 11-3 shows the interrupt level for each of the peripheral control units.

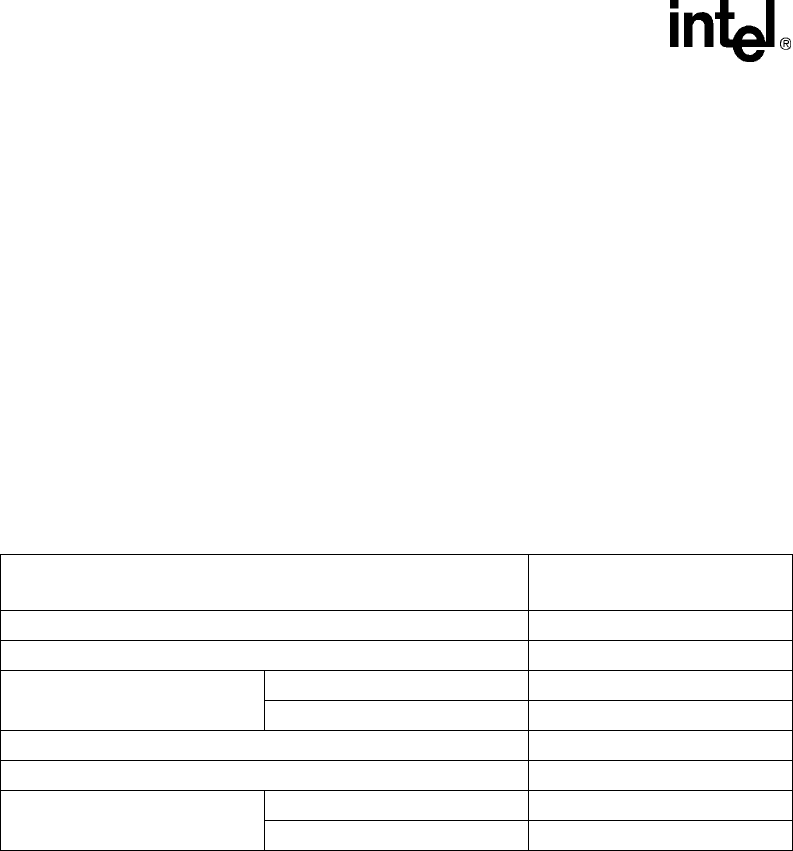

Table 11-3. Peripheral Units’ Interrupt Numbers

Peripheral

Interrupt

Number

LCD controller 12

Serial port 0: USB 13

Serial port 1:

SDLC 14

UART 15

Serial port 2: ICP 16

Serial port 3: UART 17

Serial port 4:

MCP 18

SSP 19