SA-1100 Developer’s Manual 11-141

Peripheral Control Module

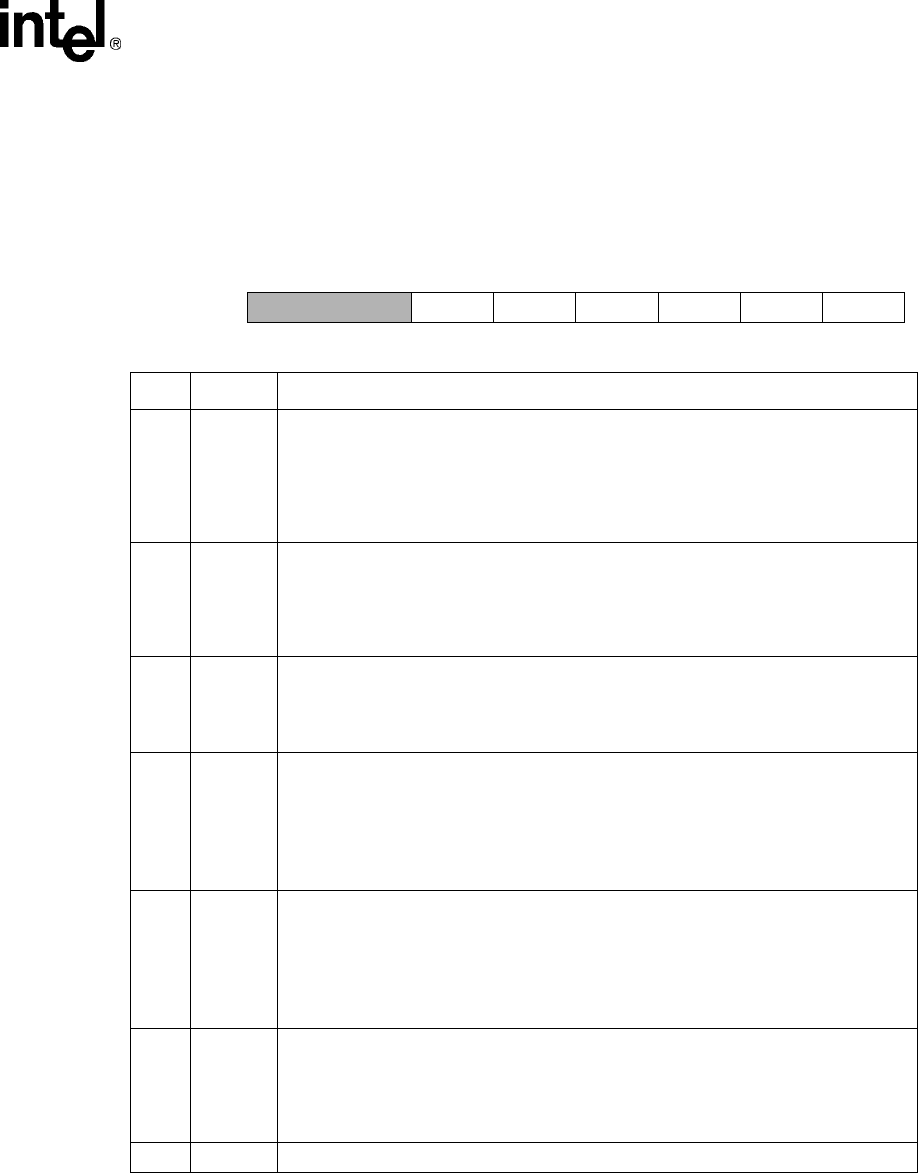

The following table shows the bit locations corresponding to the status bits within UART status

register 0. Note that the reset state of all writable status bits is unknown (indicated by question

marks) and must be cleared (by writing a one to them) before enabling the UART. Also note that

writes to reserved bits are ignored and reads return zeros.

.

Address: 0h 8005 001C UTSR0 Read/Write & Read-Only

Bit 76543210

Reserved EIF REB RBB RID RFS TFS

Reset000???00

Bit Name Description

0 TFS

Transmit FIFO service request (read-only).

0 – Transmit FIFO is more than half-full (five or more entries filled) or transmitter

disabled.

1 – Transmit FIFO is half-full (four or fewer entries filled) and transmitter operation is

enabled, DMA service request signalled, and interrupt request signalled if not masked (if

TIE=1).

1RFS

Receive FIFO service request (read-only).

0 – Receive FIFO contains seven or fewer entries of data or receiver disabled.

1 – Receive FIFO is one- to two-thirds full (contains 5, 6, 7, or 8 entries of data) or more,

and receiver operation is enabled, DMA service request signalled, and interrupt request

signalled if not masked (if RIE=1).

2RID

Receiver idle.

0 – Receiver is busy, receive FIFO is empty, or receiver is disabled.

1 – Receiver is enabled, receive FIFO not empty, 3 frame times elapsed without

receiving data, request interrupt.

3RBB

Receiver begin of break.

0 – No break detected.

1 – Null character followed by parity and stop bits containing zeroes received, request

interrupt.

Note: Setting this bit allows the setting of REB, and also prevents further null characters

with framing errors from being stored in the receive FIFO (only one stored).

4REB

Receiver end of break.

0 – No end of break detected.

1 – Beginning of break was detected (interlock set) and a rising edge detected on the

receive pin, request interrupt.

Note: Setting of this bit allows the setting of RBB, and also allows characters to once

again be stored in the receive FIFO.

5EIF

Error in FIFO (read-only).

0 – Bits 8..10 are not set within any of the four bottom entries of the receive FIFO,

receive FIFO DMA service requests are enabled.

1 – One or more error bits (8..10) are set within one or more of the bottom four entries of

the receive FIFO, request interrupt, disable receive FIFO DMA service requests.

7.. 6 — Reserved.