SA-1100 Developer’s Manual 11-33

Peripheral Control Module

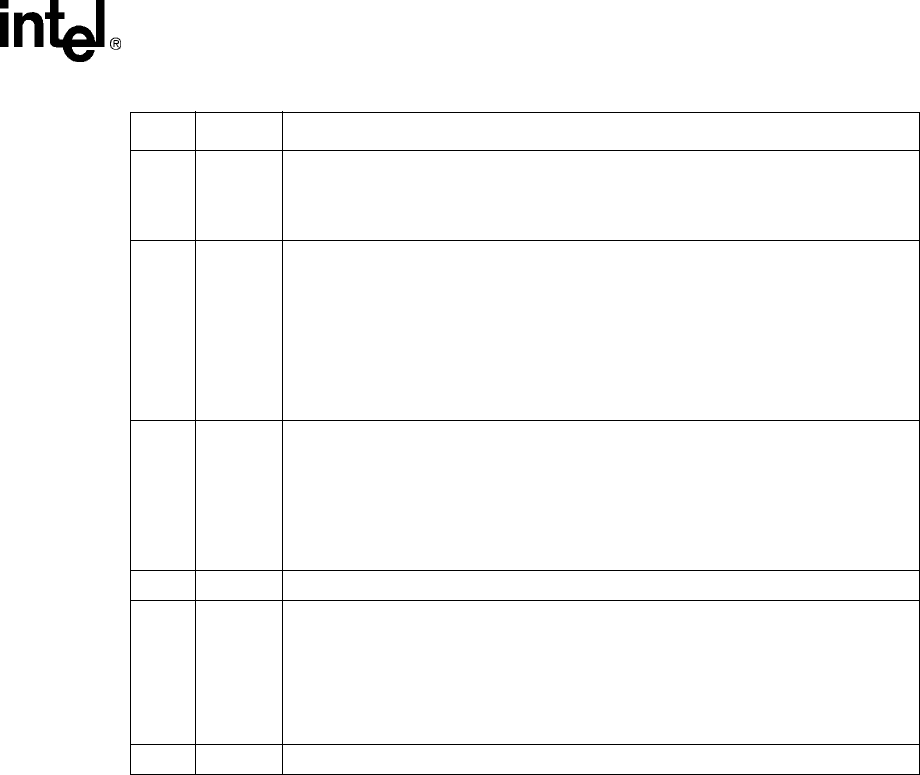

7PASPassive/active display select.

0 – Passive or STN display operation enabled. Dither logic is enabled.

1 – Active or TFT display operation enable. Dither logic bypassed, pin timing changes to

support continuous pixel clock, output enable, VSYNC, HSYNC signals.

8BLE

Big/little endian select.

0 – Little endian operation is selected, half-word palette buffer data is packed into

individual words of memory starting with the least significant half-word, and frame buffer

pixel data is packed into individual words of memory starting with the least significant

nibble, byte, or half-word.

1 – Big endian operation is selected, half-word palette buffer data is packed into

individual words of memory starting with the most significant half-word, and frame buffer

pixel data is packed into individual words of memory starting with the most significant

nibble, byte, or half-word.

9DPD

Double-pixel data pin mode.

0 – In single-panel monochrome operation, four pixels are presented to LDD<3:0> each

pixel clock.

1 – In single-panel monochrome operation, eight pixels are presented to LDD<7:0>

each pixel clock.

Note: This bit is ignored in all other modes of operation except for single-panel

monochrome.

11..10 —

Reserved.

19..12 PDD

Palette DMA request delay.

Value (from 0 to 255) used to specify the number of memory controller clocks (half the

speed of the CPU clock). The on-chip palette DMA request should be disabled after

each DMA transfer to the palette. The clock count starts after the last write of each burst

cycle. While the counter is decrementing, all DMA requests from the palette are masked.

When the counter reaches zero, any pending or subsequent DMA requests are allowed

to generate a 4-word burst. Programming PDD=8h’00 disables this function.

31..20 —

Reserved.

Bit Name Description