11-126 SA-1100

Developer’s Manual

Peripheral Control Module

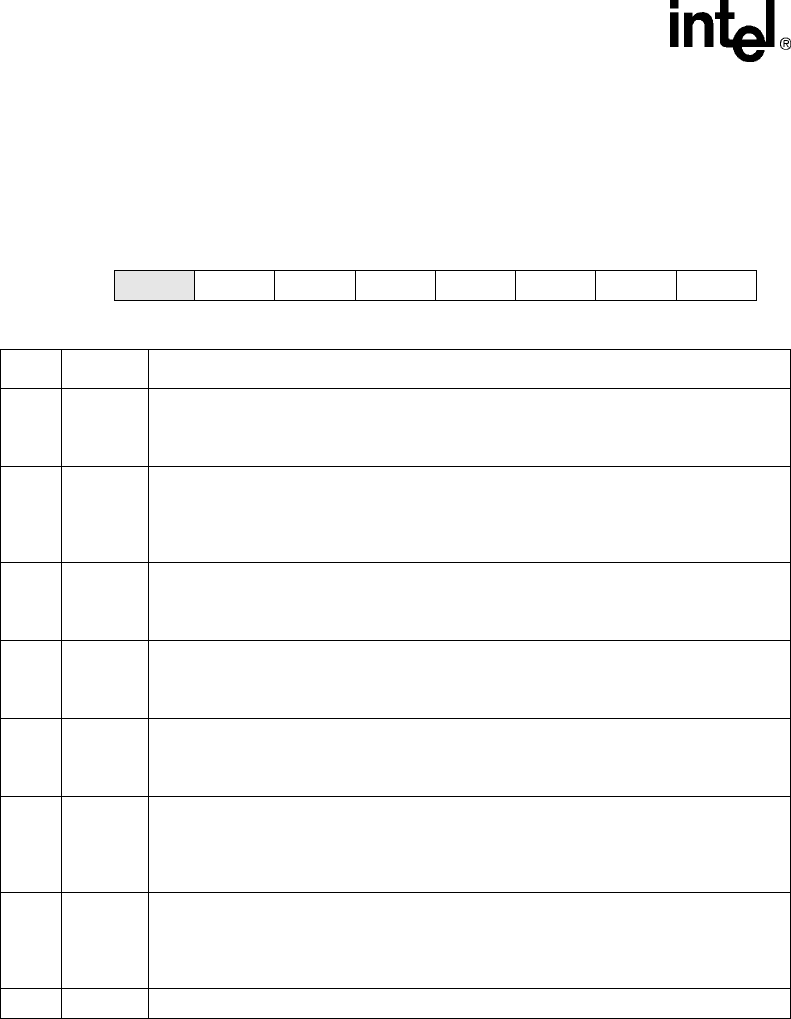

The following table shows the location of the flags within HSSP status register 1. The bits within

this register are read-only and do not produce interrupt requests. Note that writes to bit 7 are

ignored and reads return zero.

Address: 0h 8004 0078 HSSR1 Read-Only

Bit 76543210

Res. ROR CRE EOF TNF RNE TBY RSY

Reset00001000

Bit Name Description

0RSY

Receiver synchronized flag (read-only).

0 – Receiver is in hunt more or is disabled.

1 – Receiver logic is synchronized with the incoming data (no interrupt generated).

1TBY

Transmitter busy flag (read-only).

0 – Transmitter is idle (continuous preambles) or disabled.

1 – Transmit logic is currently transmitting a frame (address, control, data, CRC, or

start/stop flag); no interrupt generated.

2 RNE

Receive FIFO not empty (read-only).

0 – Receive FIFO is empty.

1 – Receive FIFO is not empty (no interrupt generated).

3TNF

Transmit FIFO not full (read-only).

0 – Transmit FIFO is full.

1 – Transmit FIFO is not full (no interrupt generated).

4EOF

End of frame (read-only).

0 – Current frame has not completed.

1 – The value at the bottom of the receive FIFO is the last byte of data within the frame.

5 CRE

CRC error (read-only).

0 – No CRC check errors encountered in the receipt of data.

1 – CRC calculated on the incoming data. Does not match CRC value contained within

the received frame.

6ROR

Receive FIFO overrun (read-only).

0 – Receive FIFO has not experienced an overrun.

1 – Receive logic attempted to place data into receive FIFO while it was full; the next data

value in the FIFO is the last piece of “good” data before the FIFO was overrun.

7 — Reserved.