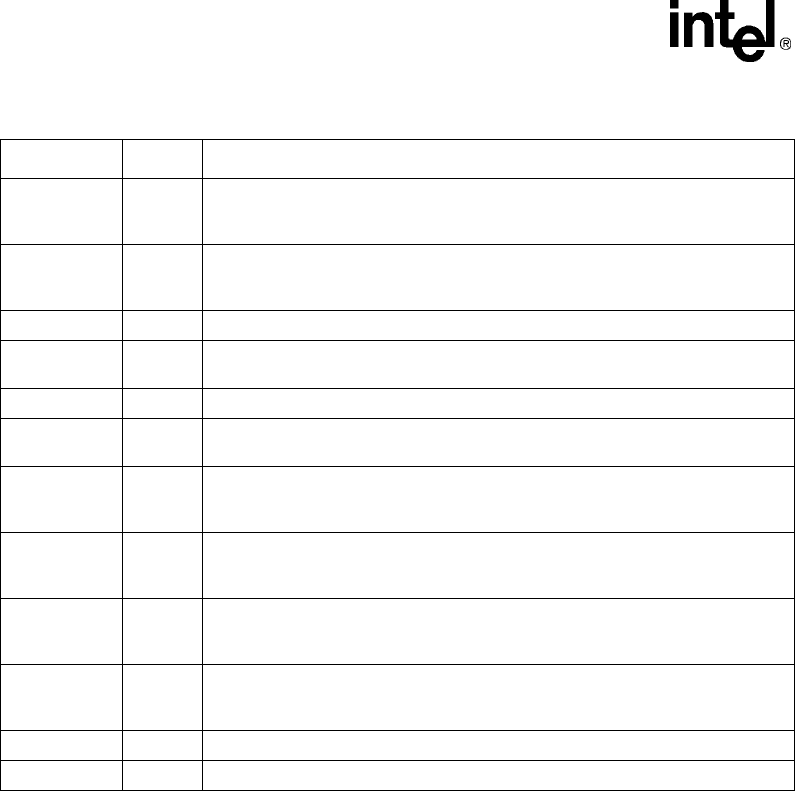

2-6 SA-1100

Developer’s Manual

Functional Description

nRESET_OUT OCZ Reset out. This signal is asserted when nRESET is asserted and deasserts when

the processor has completed resetting. nRESET_OUT is also asserted for "soft"

reset events (sleep and watchdog).

nTRST IC Test interface reset. Note this pin has an internal pull-down resistor and must be

driven high to enable the JTAG circuitry. If left unconnected, this pin is pulled low

and disables JTAG operation.

TDI IC JTAG test interface data input. Note this pin has an internal pull-up resistor.

TDO OCZ JTAG test interface data output. Note this pin does

not

have an internal pull-up

resistor.

TMS IC JTAG test interface mode select. Note this pin has an internal pull-up resistor.

TCK IC JTAG test interface reference clock. This times all the transfers on the JTAG test

interface. Note this pin has an internal pull-down resistor.

TCK_BYP IC Test clock PLL bypass. When TCK_BYP is high, the TESTCLK is used as the

core clock in place of the PLL clock; when low, the internal PLL output is used.

This signal has no relation to the JTAG TCK pin.

TESTCLK IC Test clock. TESTCLK is used to provide the core clock when TCK_BYP is high. It

should be tied low if TCK_BYP is low. This pin should be used for test purposes

only. An end user should ground this pin.

VDD — Positive supply for the core. Nine pins are allocated to this supply; eight pins are

labeled VDD. The ninth pin, labeled VDDP is dedicated to the PLL supply and

should be tied directly to the VDD power plane with the other eight VDD pins.

VDDX — Positive supply for the pins. Twenty pins are allocated to VDDX, labeled VDDX1,

VDDX2 and VDDX3. All of these pins should be tied directly to the VDDX power

plane.

VSS — Ground supply. Nine pins are allocated to VSS, including one for the PLL.

VSSX — Ground supply for the I/O pins. Eighteen pins are allocated to VSSX.

Table 2-1. Signal Descriptions (Sheet 3 of 3)

Name Type Description