SA-1100 Developer’s Manual 11-133

Peripheral Control Module

11.11.3.7 Transmit Clock Edge Select (TCE)

When SCE=1, the transmit clock edge select (TCE) bit is used to select which edge of the clock

input from the GPIO pin to use (rising or falling) to synchronously drive data onto the transmit pin.

When TCE=0, each bit transmitted is driven on the rising edge of the sample input clock; when

TCE=1, bits are driven on the clock’s falling edge. Note that the internal baud rate generator is not

used in this mode. TCE is ignored when SCE=0.

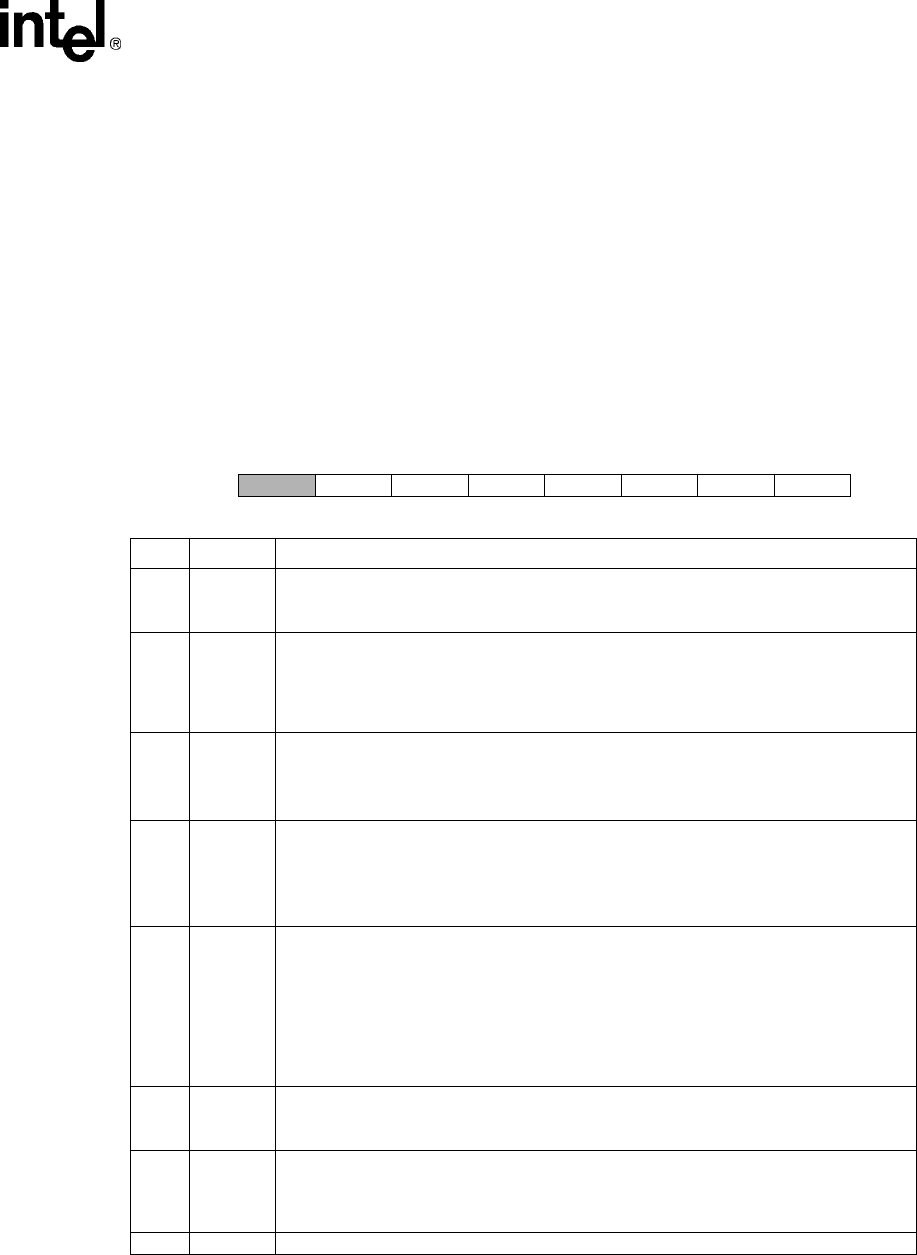

The following table shows the bit locations corresponding to the seven different control bit fields

within UART control register 0. The UART must be disabled (RXE=TXE=0) when changing the

state of any bit within this register. The reset state of these control bits is unknown (indicated by

question marks) and must be initialized before enabling the UART. Note that writes to bit 7 are

ignored and reads return zero.

Address: 0h 8005 0000 UTCR0 Read/Write

Bit 76543210

Res TCE RCE SCE DSS SBS OES PE

Reset0???????

Bit Name Description

0PE

Parity enable.

0 – Parity checking on received data and parity generation on transmitted data is disabled.

1 – Parity checking on received data and parity generation on transmitted data is enabled.

1OES

Odd/even parity select.

0 – Odd parity checking/generation selected. Parity error bit set if even number of ones

counted in data field (including the parity bit).

1 – Even parity checking/generation selected. Parity error bit set if odd number of ones

counted in data field (including the parity bit).

2SBS

Stop bit select.

0 – One stop bit transmitted per frame.

1 – Two stop bits transmitted per frame.

Note: Receiver not affected by SBS; always checks for one stop bit.

3DSS

Data size select.

0 – 7-bit data.

1 – 8-bit data.

Note: For 7-bit mode, the data is right justified within the FIFO entries, the MSBs in the

receive FIFO are zero filled, and the MSBs in the transmit FIFO are ignored.

4SCE

Sample clock enable.

0 – on-chip baud rate generator and digital PLL used to transmit and receive

asynchronous data.

1 – A clock is input via GPIO pin 20 and is used synchronously to sample receive data

and drive transmit data.

Note: Serial port 1’s UART uses GPIO pin 18 for the sample clock input; serial port 2

does not support the sample clock function. The user must also program the appropriate

bits in the GPDR and GAFR registers within the system control module.

5 RCE

Receive clock edge select.

0 – Rising edge of clock input on GPIO pin 20 used to latch data from the receive pin if SCE=1.

1 – Falling edge of clock input on GPIO pin 20 used to latch data from the receive pin if SCE=1.

6TCE

Transmit clock edge select.

0 – Rising edge of clock input on GPIO pin 20 used to drive data onto the transmit pin if SCE=1.

1 – Falling edge of clock input on GPIO pin 20 used to drive data onto the transmit pin if

SCE=1.

7—

Reserved.