SA-1100 Developer’s Manual 11-35

Peripheral Control Module

11.7.4.4 Beginning-of-Line Pixel Clock Wait Count (BLW)

The 8-bit beginning-of-line pixel clock wait count (BLW) field is used to specify the number of

“dummy” pixel clocks to insert at the beginning of each line or row of pixels. After the line clock

for the previous line has been negated, the value in BLW is used to count the number of pixel

clocks to wait before starting to output the first set of pixels in the next line. BLW generates a wait

period ranging from 1 to 256 pixel clock cycles. The user should program BLW with the desired

number of pixel clocks minus one. Note that the pixel clock pin, L_PCLK, does not transition

during these “dummy” pixel clock cycles in passive display mode (pixel clock transitions

continuously in active display mode).

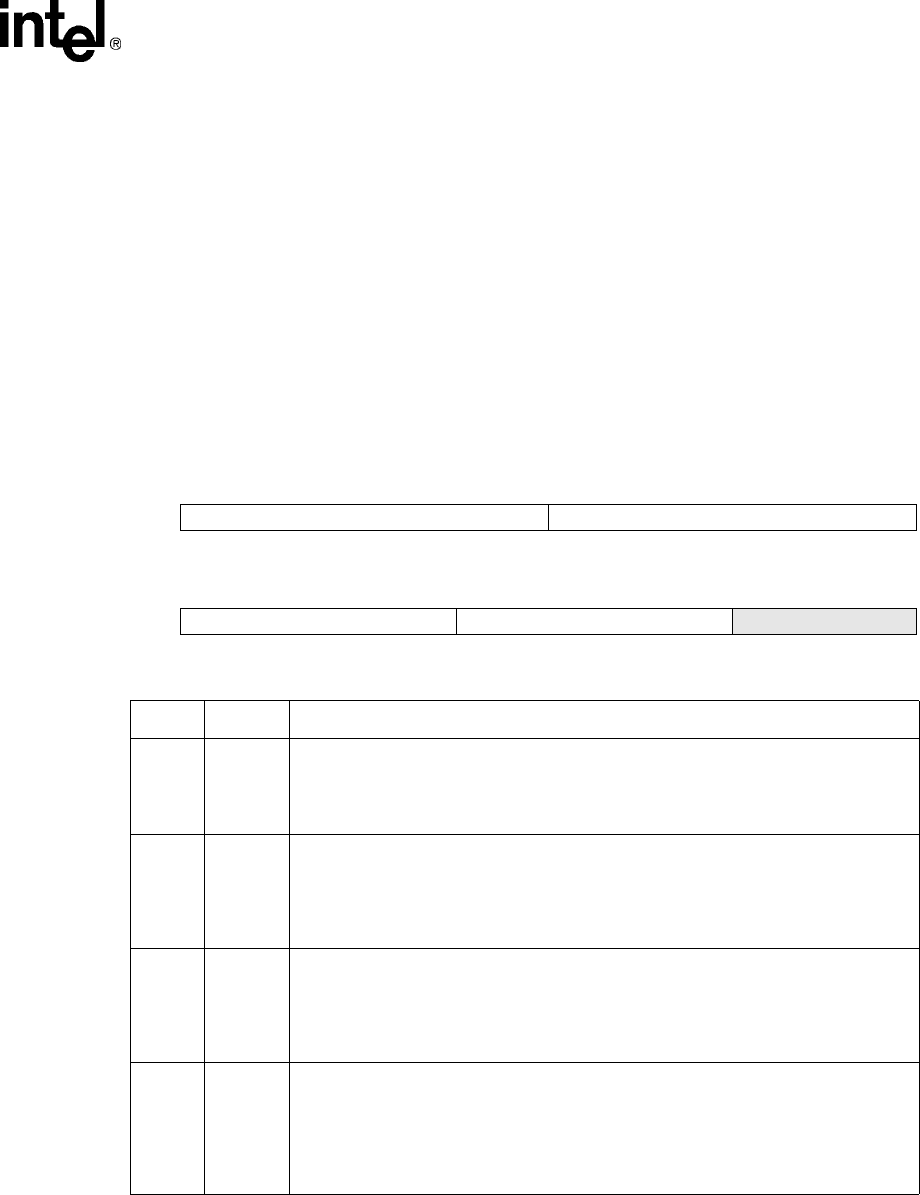

The following table shows the location of the four bit fields located in LCD control register 1

(LCCR1). The LCD controller must be disabled (LEN=0) when changing the state of any field

within this register.

Address: 0h B010 0020 LCCR1: LCD Controller Control Register 1 Read/Write

Bit31302928272625242322212019181716

BLW ELW

Reset0000000000000000

Bit1514131211109876543210

HSW PPL<9:4> PPL<3:0>

Reset0000000000000000

Bit Name Description

9..0 PPL

Pixels per line.

Value (from 1 to 1024). Used to specify number of pixels contained within each line on

the LCD display. Pixels/line = (PPL+16).

Note that PPL<3:0> are not implemented but return zeros when read.

15..10 HSW

Horizontal sync pulse width.

Value (from 1 to 64). Used to specify number of pixel clock periods to pulse the line

clock at the end of each line. HSYNC pulse width = (HSW+1).

Note that pixel clock is held in its inactive state during the generation of the line clock in

passive display mode and is permitted to transition in active display mode.

23..16 ELW

End-of-line pixel clock wait count.

Value (from 1 to 256). Used to specify number of pixel clock periods to add to the end of

a line transmission before line clock is asserted. EOL = (ELW+1).

Note that pixel clock is held in its inactive state during the end-of-line wait period in

passive display mode and is permitted to transition in active display mode.

31..24 BLW

Beginning-of-line pixel clock wait count.

Value (from 1 to 256). Used to specify number of pixel clock periods to add to the

beginning of a line transmission before the first set of pixels is output to the display.

BOL wait = (BLW+1).

Note that pixel clock is held in its inactive state during the beginning-of-line wait period

in passive display mode and is permitted to transition in active display mode.