11-156 SA-1100

Developer’s Manual

Peripheral Control Module

11.12.3.10 Loopback Mode (LBM)

The loopback mode (LBM) bit is used to enable and disable the ability of the MCP’s transmit and

receive logic to communicate. When LBM=0, the MCP operates normally. The transmit and

receive data paths are independent and communicate via their respective pins. When LBM=1, the

output of the serial shifter (MSB) is directly connected to the input of the serial shifter (LSB)

internally and control of the TXD4, RXD4, SCLK, and SFRM pins are given to the peripheral pin

control (PPC) unit.

11.12.3.11 External Clock Prescaler (ECP)

The 2-bit external clock select (ECP) field is used to divide the clock input via GPIO pin 21 when

the external clock function is enabled. When ECS=1, ECP is decoded to divide the clock input on

the GPIO<21> pin by 1, 2, 3, or 4 before being used to drive the MCP’s frame rate. When

ECP=00, the input clock is divided by 1; when ECP=01, it is divided by 2; when ECP=10, it is

divided by 3; and when ECP=11, it is divided by 4. Note that the ECP bit field is ignored when the

internal clock (ECS=0) is used to drive the MCP’s frame rate. Also note that the resultant clock

frequency after the divide has taken place can be any value within the allowable frequency range of

the UCB1100 or UCB1200 (up to 12 MHz).

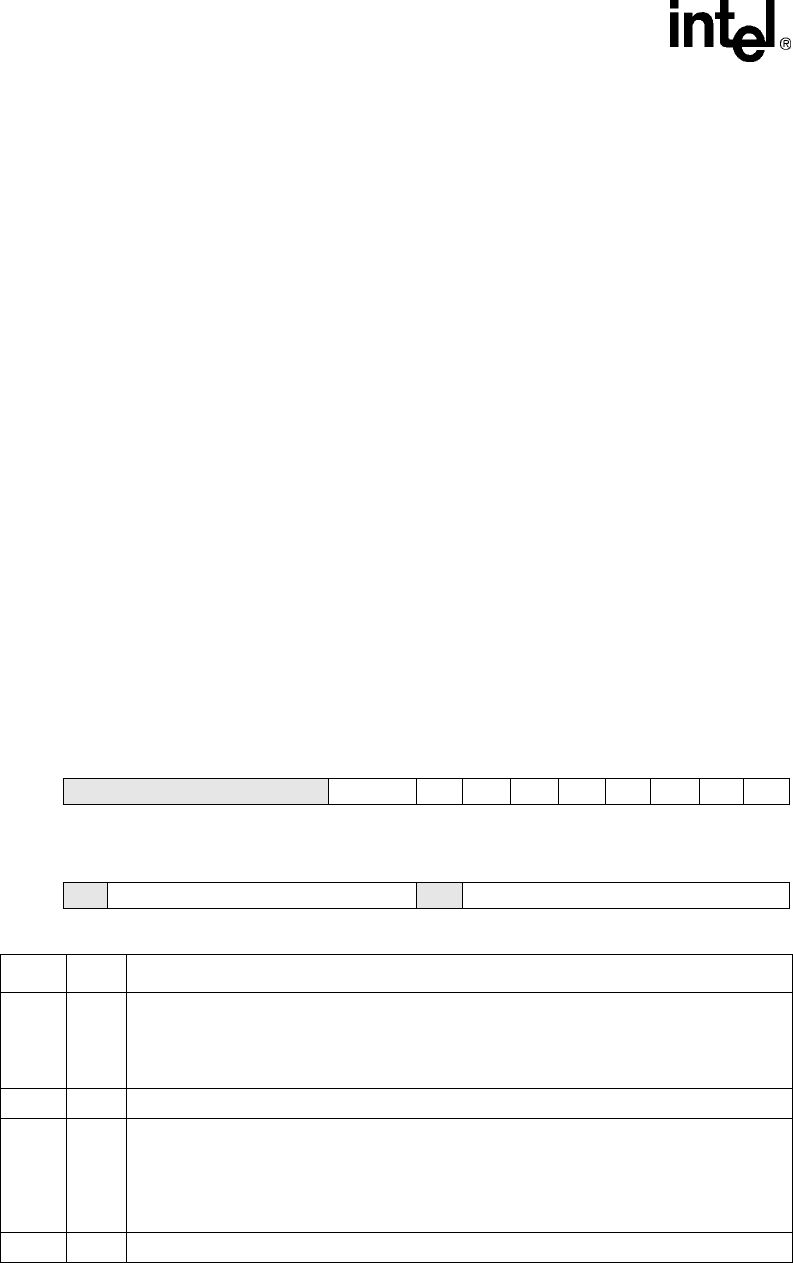

The following table shows the bit locations corresponding to the 10 different control bit fields

within the MCP control register. Note that the MCE bit is the only control bit that is reset to a

known state to ensure the MCP is disabled following a reset of the SA-1100. The reset state of all

other control bits is unknown (indicated by question marks) and must be initialized before enabling

the MCP. The user can program all 11 bit fields and enable the MCP using a single word write to

MCCR0. Writes to reserved bits are ignored and reads return zeros.

Address: 0h 8006 0000 MCP Control Register 0: MCCR Read/Write

Bit 3130292827262524232221 201918 1716

Reserved ECP LBM ARE ATE TRE TTE ADM ECS MCE

Reset00000000?? ? ??? ?0

Bit 1514131211109 8 7 6 5 4 3 2 1 0

Res. TSD Res. ASD

Reset0???????0? ? ??? ??

Bit Name Description

6..0 ASD

Audio sample rate divisor.

Value (from 6 to 127) used to match the sample rate of the audio codec within the UCB1100

or UCB1200 to time when audio D/A data should be supplied by the audio transmit FIFO.

Sample Rate = Programmed clock rate/(32xASD), where ASD is a decimal value.

7 —

Reserved.

14..8 TSD

Telecom sample rate divisor.

Value (from 16 to 127) used to match the sample rate of the telecom codec within the

UCB1100 or UCB1200 to time when telecom D/A data should be supplied by the telecom

transmit FIFO.

Sample Rate = Programmed clock rate/(32xTSD), where TSD is a decimal value.

15 —

Reserved.