CPLD: Boot and Reset Registers

10007175-02 KAT4000 User’s Manual

7-9

Register 7-12: Reset Event Register (RER) at 0xfc40,0020

R: Reserved

SHR: Software Issued Hard Reset

1 The last reset was caused by a write to the Reset Command register

WE: Watchdog Expiration

1 A reset was caused by the expiration of the watchdog timer

COPS: MPC8548 COP Soft Reset

1 A COP header soft reset (SRESET) has occurred

COPH: MPC8548 COP Hard Reset

1 A COP header hard reset (HRESET) has occurred

PAYR: Payload Reset

1 An IPMC Payload reset has occurred

PBR: Push Button Reset

1 The switch (POR_RST) caused a reset

Reset Command Register 1 (RCR1)

Reset Command registers 1 and 2 force one of several types of resets, as shown below. A

reset sequence is initiated by writing a one to a valid bit, then the bit is automatically

cleared. Set only one bit in this register at a time. If reset when in a locked state, a clock syn-

chronizer will issue a loss of lock interrupt. To prevent this, mask the interrupt from regis-

ters 0xa8, 0xaC or 0xb0. The hardware will issue resets to the clock synchronizers for 10ms.

Software must wait at least 10ms before accessing these devices. Default register values

are shown in the bottom row of the register table.

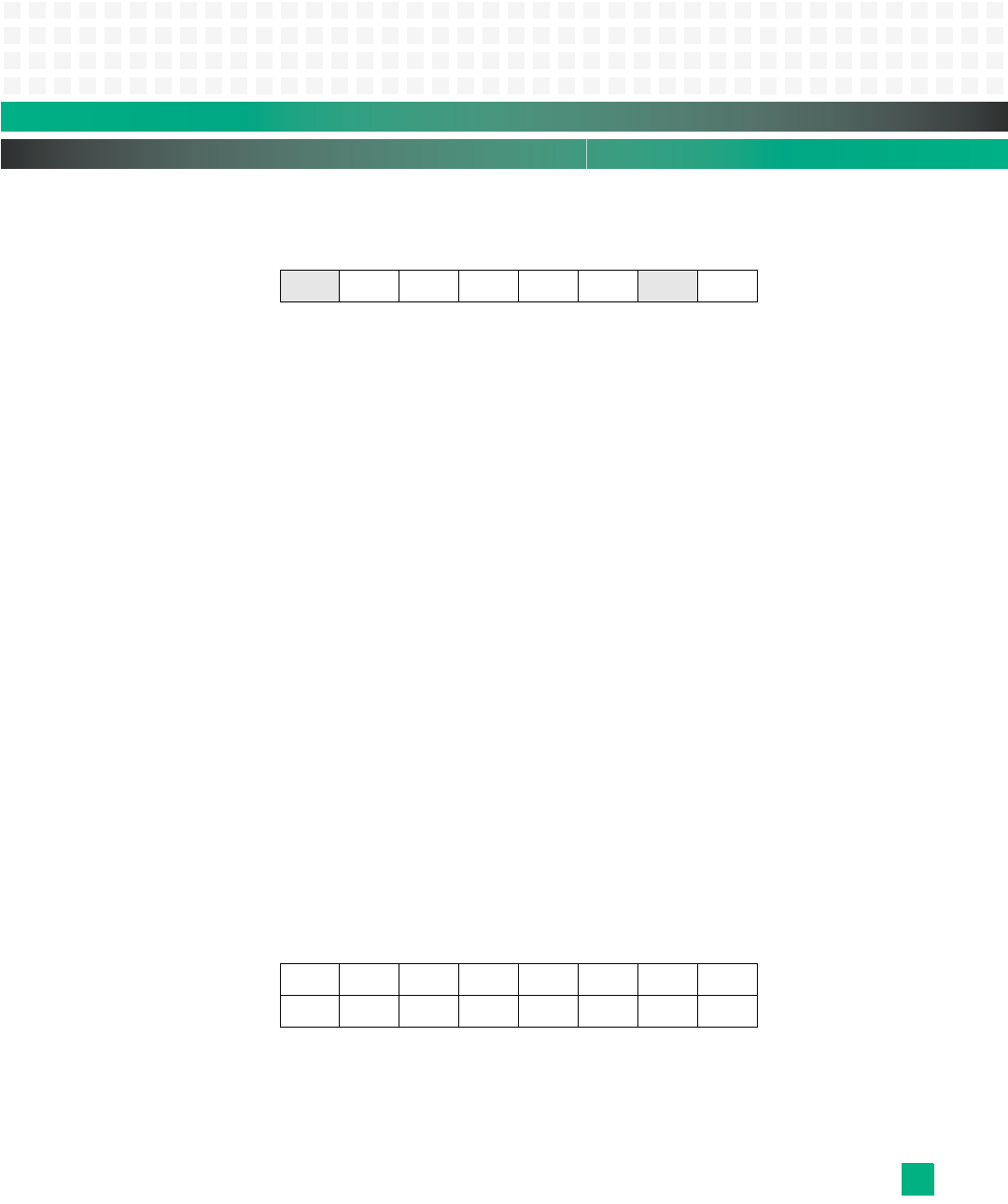

Register 7-13: Reset Command Register 1 (RCR1) at 0xfc40,0024

CPUH: CPU Hard Reset

1 Reset

0No reset (default)

76543210

RSHRWECOPS

COPH

PAYR RPBR

76543210

CPUH CSR1 CSR2 CSR3 PCIE I2C FSHR CER

00000000