CPLD: JTAG Interface

KAT4000 User’s Manual 10007175-02

7-20

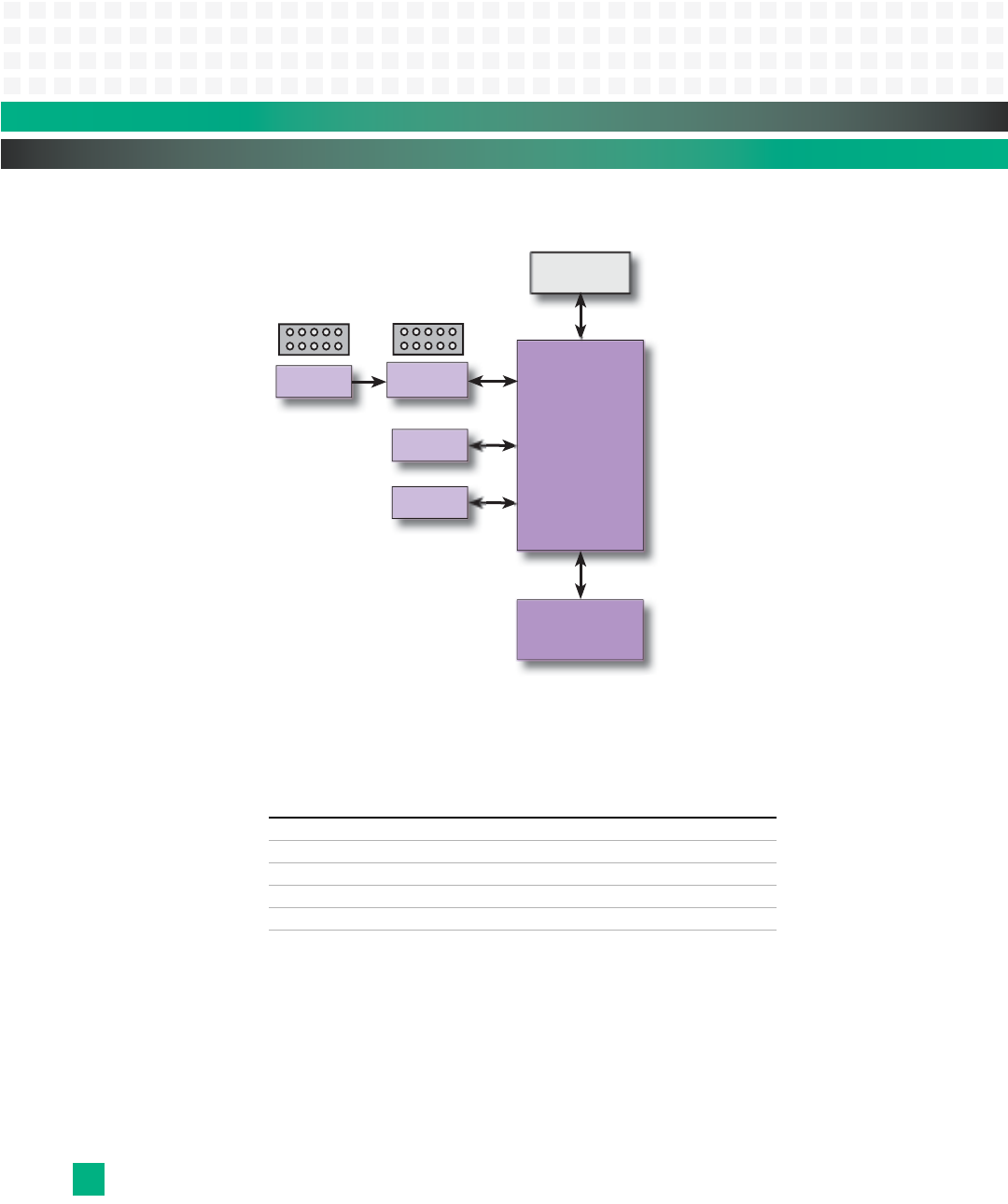

Figure 7-2: PLD JTAG Diagram

JP1 is the configuration header for PLD programming. Installing a shunt on jumper JP1, pins

1:2, enables the JP3 PLD programming header. The header pin assignments are defined in

Table 7-3.

Table 7-3: JP1 Pin Assignments

Shunt Description:

1:2 TRANS: Enable programming via header (enables CPU JTAG/COP access)

3:4 LSBSEL0: Select KSL PLD

5:6 LSBSEL1: Select AMC Site 1

7:8 LSBSEL5: Select Fat Pipe Module

9:10 LSBSEL6: Select IPMC PLD

AMC 1

SCANSTA112

JTAG Multiplexer

SCANSCA112

JTAG

Multiplexer

Master

Port 1

Port 2

Port 3

Port 4

Port 5

Port 6

Port 0

KSL PLD

IPMC PLD

Programming

Header JP3

Fat Pipe

Switch Module

Config.

Header JP1