Overview: Physical Memory Map

KAT4000 User’s Manual 10007175-02

1-6

PHYSICAL MEMORY MAP

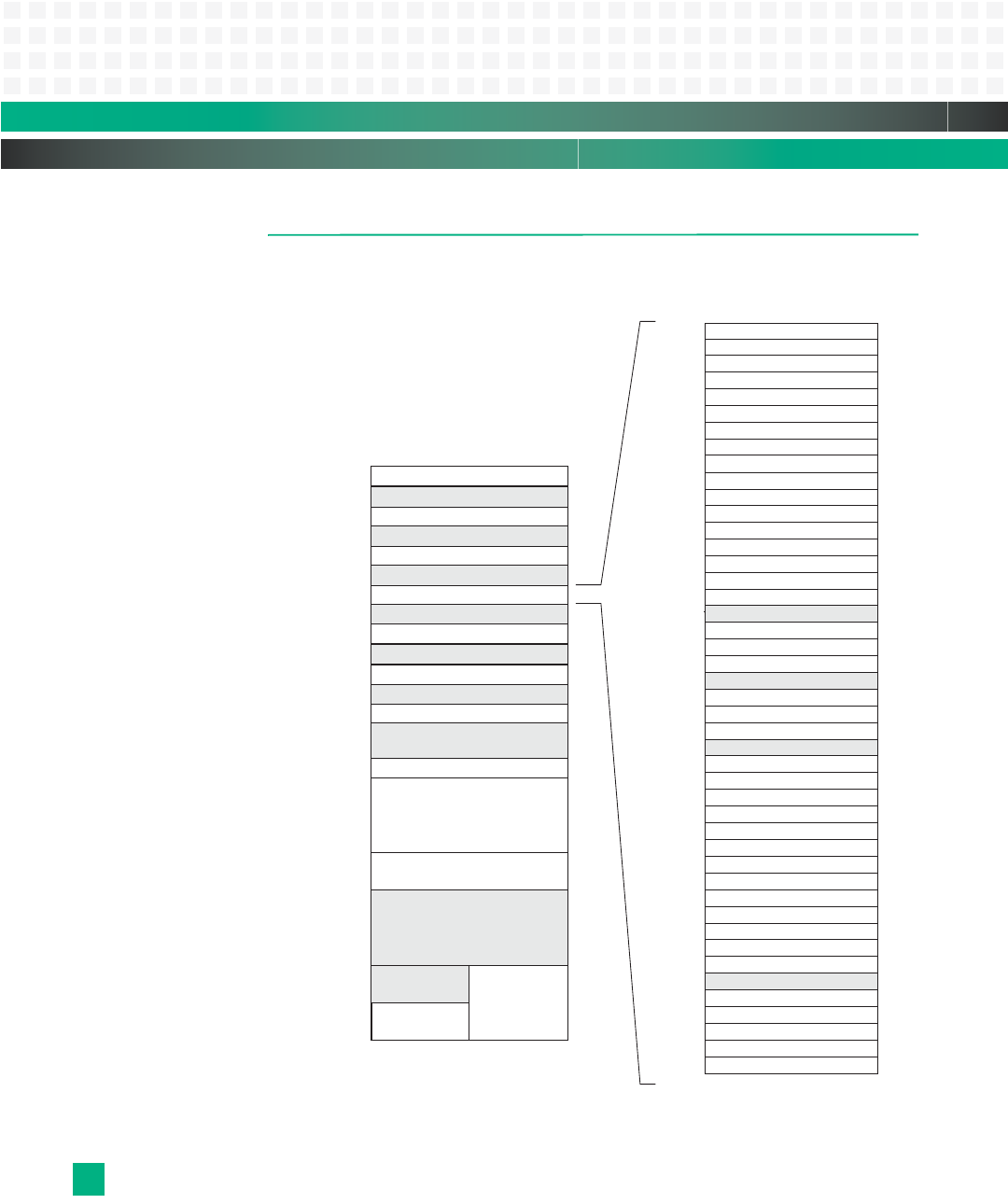

Fig. 1-2 illustrates the KAT4000 memory map:

Figure 1-2: KAT4000 Memory Map

8000,0000

FC12,0000

FC00,0000

FC80,0000

FC88,0000

FFFF,FFFF

Hex Address

0000,0000

CPLD Registers (512 KB)

NAND Flash (32 KB)

FFF0,0000

Socketed Flash (if installed) (512 KB)

Boot Area (1 MB)

Reserved

Reserved

CCSRBAR (MPC8548 Registers, 1 MB)

FF70,0000

FF80,0000

A000,0000

PCI Express Switch

(if installed) (512 MB)

NOR Flash (32 MB)

E000,0000

Reserved

FC48,0000

Reserved

E200,0000

Reserved

Hex Address

FC40,0028

Scratch Register 1

Boot Device Redirection Register

Clock Sync. Control Register 2

Clock Control, AMC4 CLK1 Register

Clock Control, AMC4 CLK2 Register

Clock Control, AMC1 CLK1 Register

Clock Sync. Primary Source 1

Clock Sync. Primary Source 2

Clock Control, AMC3 CLK3 Register

Clock Control, AMC3 CLK2 Register

FC40,0040

FC40,0044

FC40,004C

FC40,0050

FC40,0054

FC40,0058

FC40,005C

FC40,0060

FC40,0064

FC40,0068

FC40,006C

FC40,0070

FC40,0074

FC40,0048

MISC Control Register

Clock Sync. Control Register 1

Clock Sync. Control Register 3

Clock Control, AMC1 CLK2 Register

Clock Control, AMC1 CLK3 Register

Clock Control, AMC2 CLK1 Register

Clock Control, AMC2 CLK2 Register

Clock Control, AMC2 CLK3 Register

Clock Control, AMC4 CLK3 Register

FC40,002C

FC40,0030

FC40,0034

FC40,0038

FC40,003C

FC40,0078

FC40,007C

FC40,0080

FC40,0084

FC40,0088

Clock Control, aTCA CLK3 A Register

FC40,008C

FC40,0000

FC40,0004

FC40,0024

FC40,0020

FC40,001C

FC40,0018

FC40,0014

FC40,0010

FC40,000C

FC40,0008

FC40,0090

Product ID Register

Hardware Version Register

PLD Version Register

PLL Configuration Register

Hardware Config. Register 0

Jumper Settings Register

LED Control Register

Reset Event Register

Reset Command Register 1

Reset Command Register 2

Reserved

Clock Sync. Primary Source 3

Reserved

Clock Control, AMC3 CLK1 Register

Reserved

RTM GPIO State Register

RTM GPIO Control Register

Clock Sync. Secondary Source 1

Clock Sync. Secondary Source 2

Clock Sync. Secondary Source 3

Reserved

Clock Control, aTCA CLK3 B Register

Clock Sync. Interrupt Register 1

Clock Sync. Interrupt Register 2

Clock Sync. Interrupt Register 3

FC40,0094

FC40,0098

FC40,009C

FC40,00A0

FC40,00A4

FC40,00A8

FC40,00AC

FC40,00B0

1FFF,FFFF

3FFF,FFFF

Reserved

SDRAM

DDR2

(512 MB)

SDRAM

DDR2

(1 GB)

PCIe Switch or sRIO Fat Pipe Module

(if installed) (1 GB)

FC14,0000

FC18,0000

FC40,0000

Reserved

Ethernet Core Switch Registers (128 KB)

FC10,0000

Reserved

FC00,8000

Reserved

Fat Pipe Switch Registers

(if installed) (256 KB)