Central Processing Unit: Interrupts and Exception Processing

10007175-02 KAT4000 User’s Manual

3-9

Noncritical: The processor is able to change program flow to handle conditions generated by external

signals, errors, or unusual conditions. The Save and Restore registers, SRR0/SRR1, save

state when they are taken and use the rfi instruction to restore state. The external interrupt

enable bit, MSR[EE], can mask these asynchronous interrupts.

Critical: The Critical Save and Restore registers, CSRR0/CSRR1, save state when they are taken dur-

ing a noncritical interrupt or regular program flow and use the rfci instruction to restore

state. The critical enable bit, MSR[CE], can mask these interrupts. This interrupt also

includes watchdog timer time-out inputs.

Machine State Register

The Machine State register (MSR) configures the state of the MPC8548. On initial power-up

of the KAT4000, most of the MSR bits are cleared. Please refer to the MPC8548 PowerQuicc

III Integrated Communications Processor Reference Manual for more detailed descriptions of

the individual bit fields.

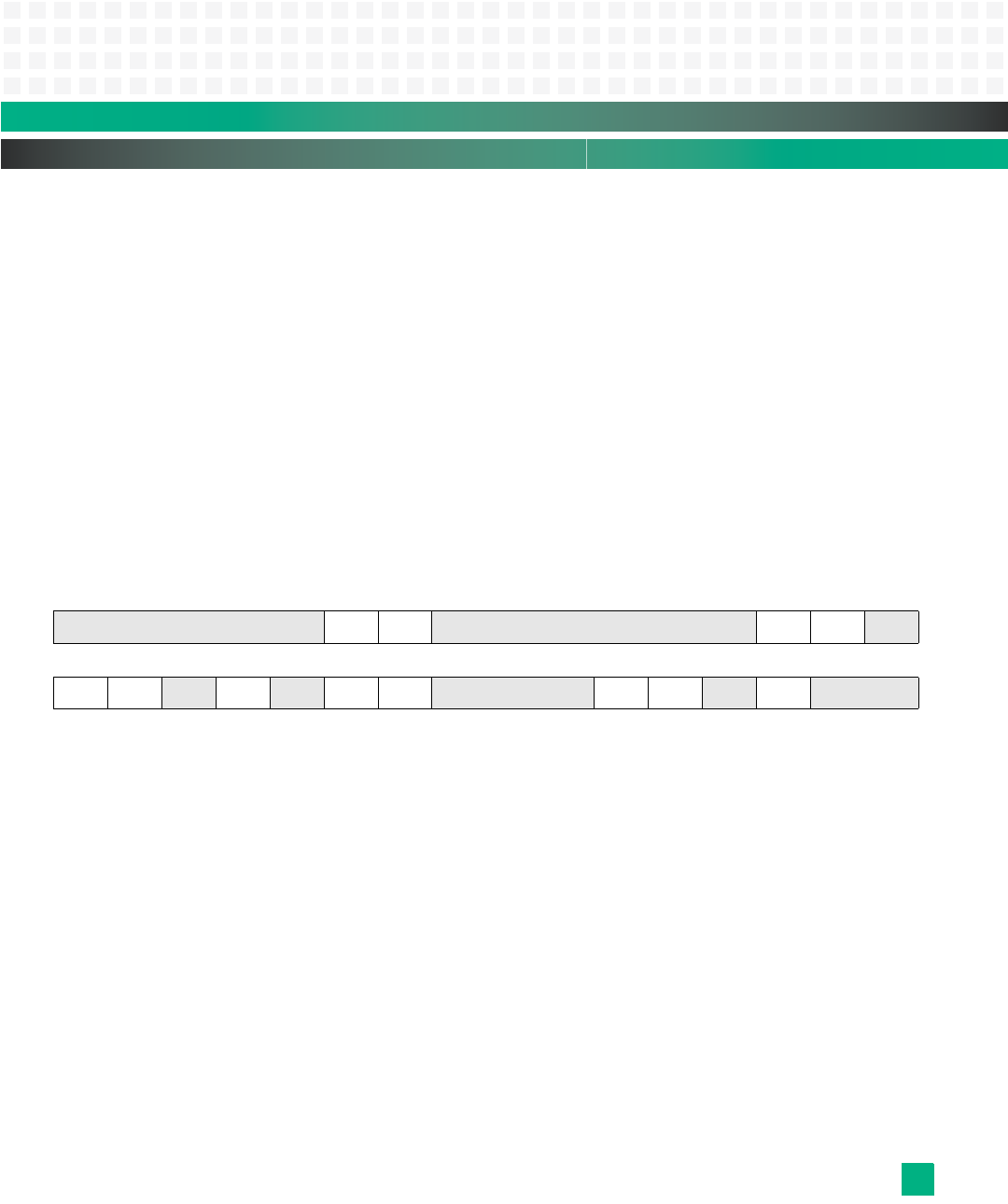

Register 3-4: CPU Machine State Register (MSR)

R: Reserved should be cleared.

UCLE: User-mode Cache Lock Enable—restricts user-mode cache-line locking by the operating sys-

tem.

0 Any cache lock instruction takes a cache-locking DSI exception

1 A cache-locking DSI is not taken

SPE: Signal Processing Engine enable

0 An SPE APU unavailable exception occurs

1 Software can execute supported SPE and SPFP APU instructions

WE: Wait state Enable—allows the core complex to signal a request for power management.

0 CPU continues processing

1 CPU enters wait state

CE: Critical Enable

0 Critical input and watchdog timer interrupts disabled

1 Critical input and watchdog timer interrupts enabled

32 36 37 38 39 44 45 46 47

reserved

UCLE

SPE reserved WE CE R

48 49 50 51 52 53 54 55 57 58 59 60 61 62 63

EE PR RMER

UBLE

DE reserved IS D RPM reserved