CPLD: Clock Synchronizer Registers

10007175-02 KAT4000 User’s Manual

7-13

CLOCK SYNCHRONIZER REGISTERS

Clock Synchronizer Control Registers 1-3 (CSC1—CSC3)

The Clock Synchronizer Control registers control the functionality of the clock synchronizer

devices. Default is 0x40 for register 1 and 0x00 for registers 2 and 3.

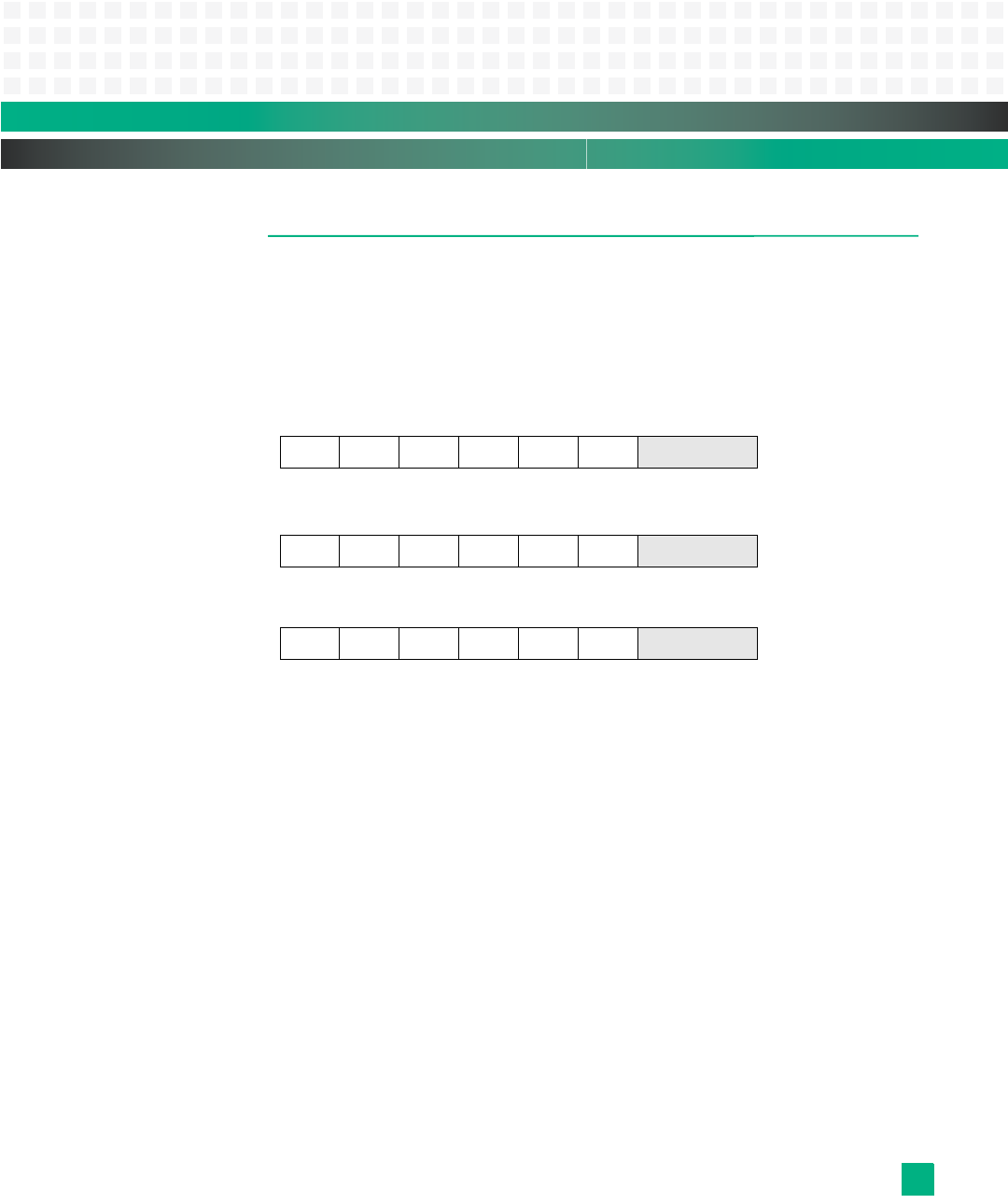

Register 7-16: Clock Synchronizer Control Registers 1-3 (CSC1-CSC3) at 0xfc40,0040, 0xfc40,0044, 0xfc40,0048,

respectively

Default register values for CSC1are shown in the following row.

Default register values for CSC2 and CSC3 are shown in the following row.

FS2, FS1: Input Frequency Select

00 19.44 MHz

01 8 KHz

10 1.544 MHz

11 2.048 MHz

MS2, MS1: Mode Select

00 Normal

01 Holdover

10 Freerun

11 Reserved

PCCI: Phase Continuity Control Input

Controls state changes between Holdover and Normal modes. Please refer to Chapter 7 for

further details.

RSEL: Input Reference Select

1 Secondary Clock

0Primary Clock

R: Reserved

76543210

FS2 FS1 MS2 MS1 PCCI RSEL reserved

010000

000000