Central Processing Unit: Interrupts and Exception Processing

KAT4000 User’s Manual 10007175-02

3-8

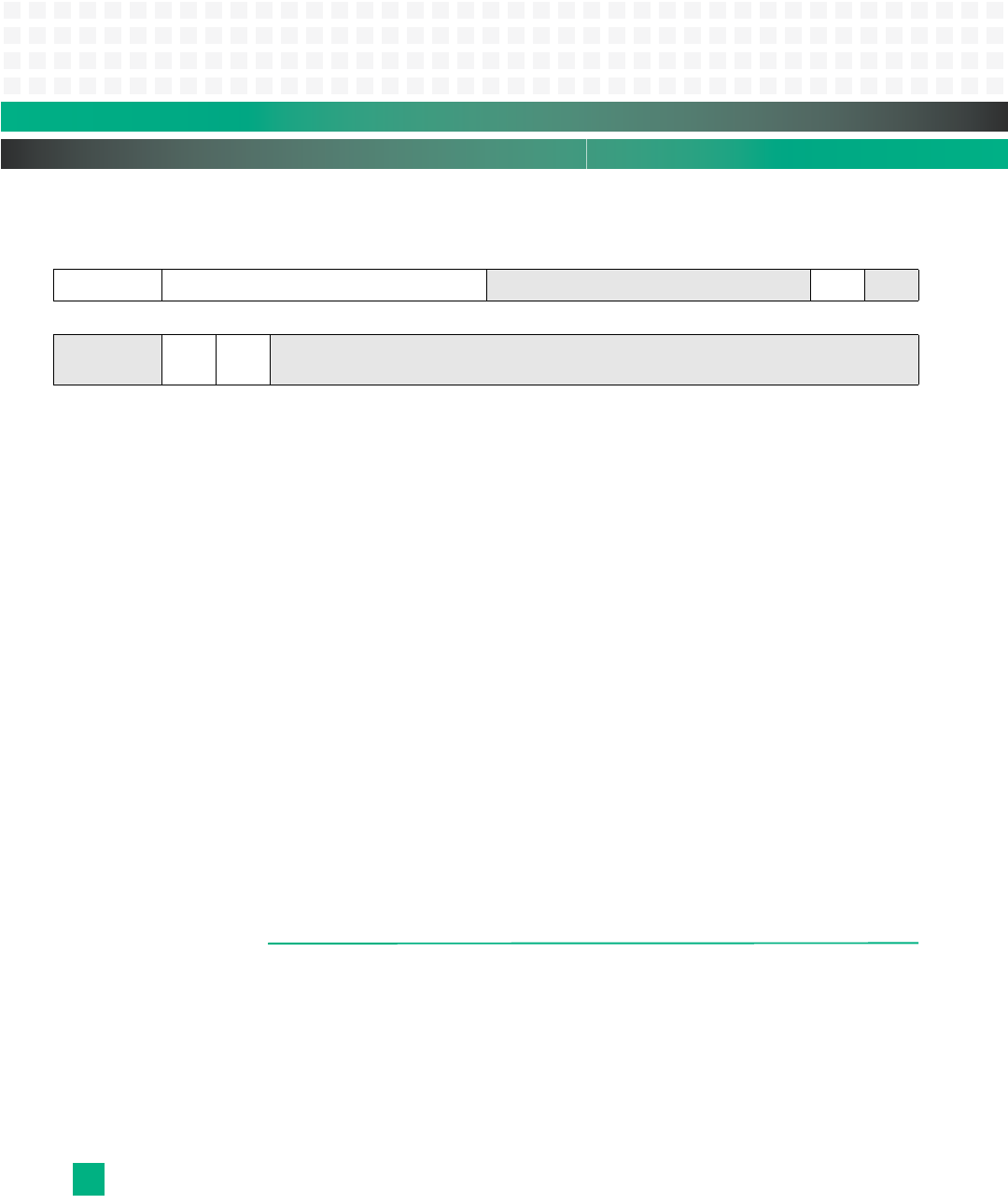

Register 3-3: MPC8548 Hardware Implementation Dependent Register 1 (HID1)

PLL_MODE: Read-only for integrated devices

01 Fixed value for MPC8548

PLL_CFG: This is reflected directly from configuration input pins (read-only). PLL_CFG[0-4] corre-

sponds to the integer divide ratio and PLL_CFG is the half-mode bit.

00010 0 ratio of 2:1

00010 1 ratio of 5:2 (2.5:1)

00011 0 ratio of 3:1

00011 1 ratio of 7:2 (3.5:1)

R: Reserved should be cleared.

RFXE: Read Fault Exception Enable—controls whether assertion of core_fault_in causes a machine

check interrupt.

0 Assertion of core_fault_in cannot cause a machine check

1 A machine check can occur due to assertion of core_fault_in

ASTME: Address bus Streaming Mode Enable

0 Mode disabled

1 Mode enabled

ABE: Address Broadcast Enable for dcbf, dcbst, dcbi, dcbic, icbic, mbar, msync, tlbsync

0 Disable address broadcasting for cache and TLB control operations

1 Enable address broadcasting for cache and TLB control operations

INTERRUPTS AND EXCEPTION PROCESSING

The interrupt process begins when an exception occurs. The MPC8548 e500 core processes

three types of interrupts: machine check, critical, or noncritical. Each interrupt type has

separate control and status register sets as listed in the following priority:

Machine Check (highest priority):

Machine Check Save and Restore registers (MCSRR0/MCSRR1) save state when they are

taken, and use rfmci instruction to restore state. The machine check enable bit, MSR[ME],

can mask these interrupts.

32 33 34 39 40 45 46 47

PLL_MODE PLL_CFG reserved

RFXE

R

48 49 50 51 52 63

reserved AST

ME

ABE reserved