Central Processing Unit: MPC8548 Exception Handling

10007175-02 KAT4000 User’s Manual

3-13

SYSCLK: System Clock is the primary clock input to the e500 core and all the devices and interfaces

that operate synchronously with the core.

RTC: Real-Time Clock is an input to the MPC8548. Optionally, it can be used to clock the e500

core timer facilities and by the MPC8548 PIC global timer facilities.

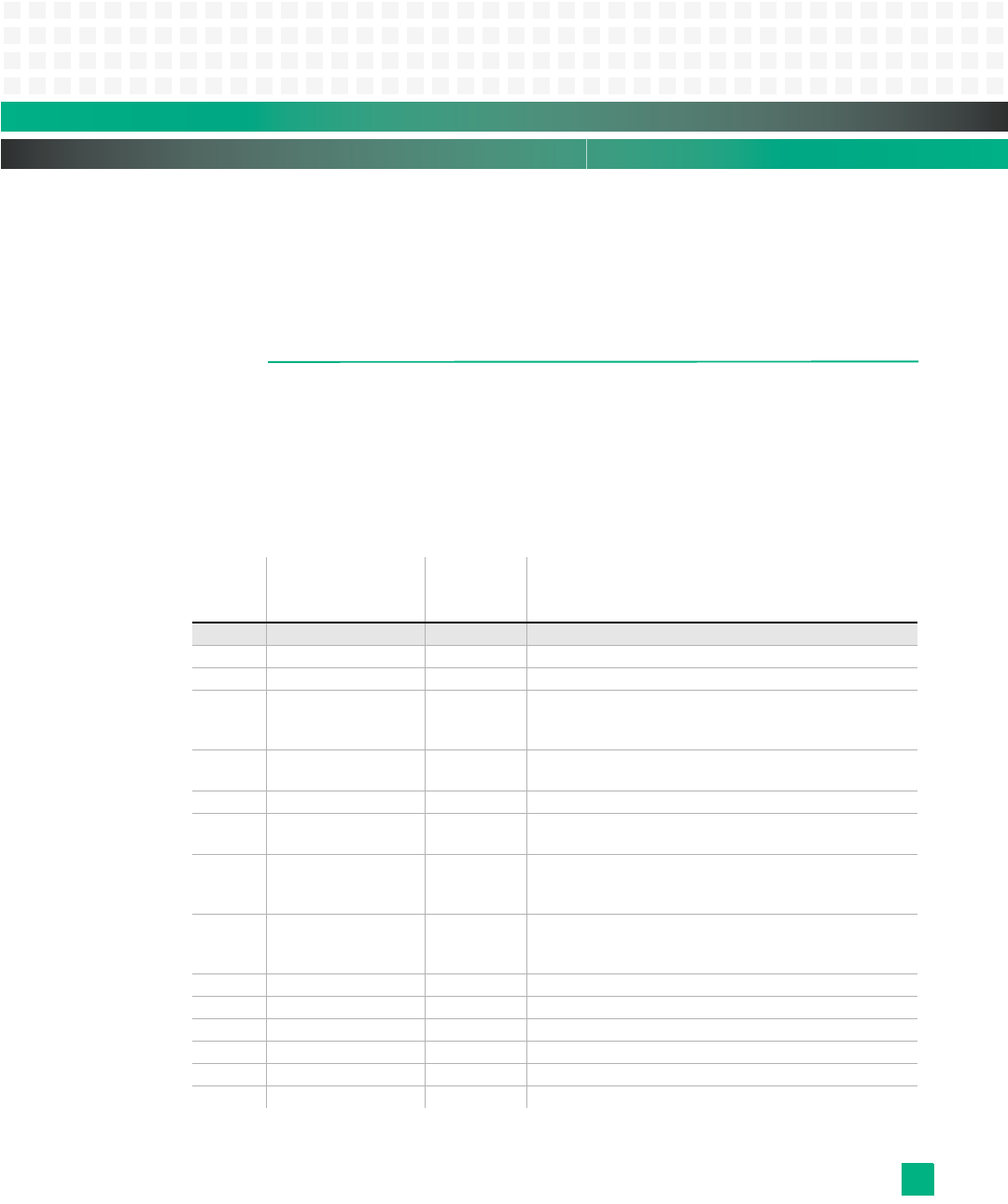

MPC8548 EXCEPTION HANDLING

Each type of CPU exception transfers control to a different address in the vector table. The

vector table normally occupies the first 8 kilobytes of RAM (with a base address of

0000,0000

16

) or Flash (with a base address of E000,0000

16

). An unassigned vector position

may be used to point to an error routine or for code or data storage.

Tab le 3 -5 lists the exceptions recognized by the MPC8548 and the conditions that cause

them.

Table 3-5: MPC8548 Exceptions

IVOR: Type:

Vector

Offset Hex

Address: Notes:

reserved 00000 —

IVOR0 Critical Input 00100 Caused when MSR[CE]=1

IVOR1 Machine Check 00200 Caused when MSR[ME]=1

IVOR2 Data Storage

Interrupt (DSI)

00300 Caused by one of the following exception conditions: read

access control, write access control, byte-ordering, cache

locking or storage synchronization

IVOR3 Instruction Storage

Interrupt (ISI)

00400 Caused by one of the following exception conditions:

execute access control or byte-ordering

IVOR4 External Interrupt 00500 Caused when MSR[EE]=1

IVOR5 Alignment 00600 Caused when the processor core cannot perform a

memory access

IVOR6 Program Check 00700 Caused by one of the following exception conditions:

illegal instruction, privileged instruction, trap or

unimplemented operation

IVOR7 Floating-Point

Unavailable

00800 If MSR[FP]=0, the floating point registers are disabled and

attempting to execute any floating point instruction

causes a floating point unavailable exception

IVOR8 System Call 00900 Caused by the execution of a System Call (sc) instruction

IVOR10 Decrementer 00A00 Caused when TSR[DIS]=1, TCR[DIE]=1 and MSR[EE]=1

IVOR11 Interval Timer 00B00 Caused when TSR[FIS]=1, TCR[FIE]=1 and MSR[EE]=1

IVOR12 Watchdog Timer 00C00 Caused when TSR[WIS]=1, TCR[WIE]=1 and MSR[CE]=1

IVOR13 Data TLB Error 00D00 Caused by a Data TLB Miss exception condition

IVOR14 Instruction TLB Error 00E00 Caused by an Instruction TLB Miss exception condition