Epson Research and Development

Page 105

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

bits 5-0 VRTC/FPFRAME Start Position Bits [5:0]

For CRT and TFT/D-TFD, these bits specify the delay in lines from the start of the vertical non-dis-

play period to the leading edge of the VRTC pulse and FPFRAME pulse respectively. For passive

LCD, FPFRAME is automatically created and these bits have no effect.

VRTC/FPFRAME start position (lines) = VRTC/FPFRAME Start Position Bits [5:0] + 1

The maximum start delay is 64 lines.

Note

This register must be programmed such that

(REG[0Ah] bits [5:0] + 1)

≥

(REG[0Bh] + 1) + (REG[0Ch] bits [2:0] + 1)

For exact timing please use the timing diagrams in section 7.5

bit 7 VRTC Polarity Select

This bit selects the polarity of the VRTC pulse to the CRT.

When this bit = 1, the VRTC pulse is active high.

When this bit = 0, the VRTC pulse is active low.

bit 6 FPFRAME Polarity Select

This bit selects the polarity of the FPFRAME pulse to the TFT/D-TFD or passive LCD.

When this bit = 1, the FPFRAME pulse is active high for TFT/D-TFD and active low for passive.

When this bit = 0, the FPFRAME pulse is active low for TFT/D-TFD and active high for passive.

bits 2-0 VRTC/FPFRAME Pulse Width Bits [2:0]

For CRT and TFT/D-TFD, these bits specify the pulse width of VRTC and FPFRAME respectively.

For passive LCD, FPFRAME is automatically created and these bits have no effect.

VRTC/FPFRAME pulse width (lines) = VRTC/FPFRAME Pulse Width Bits [2:0] + 1

Note

This register must be programmed such that

(REG[0Ah] bits [5:0] + 1)

≥

(REG[0Bh] + 1) + (REG[0Ch] bits [2:0] + 1)

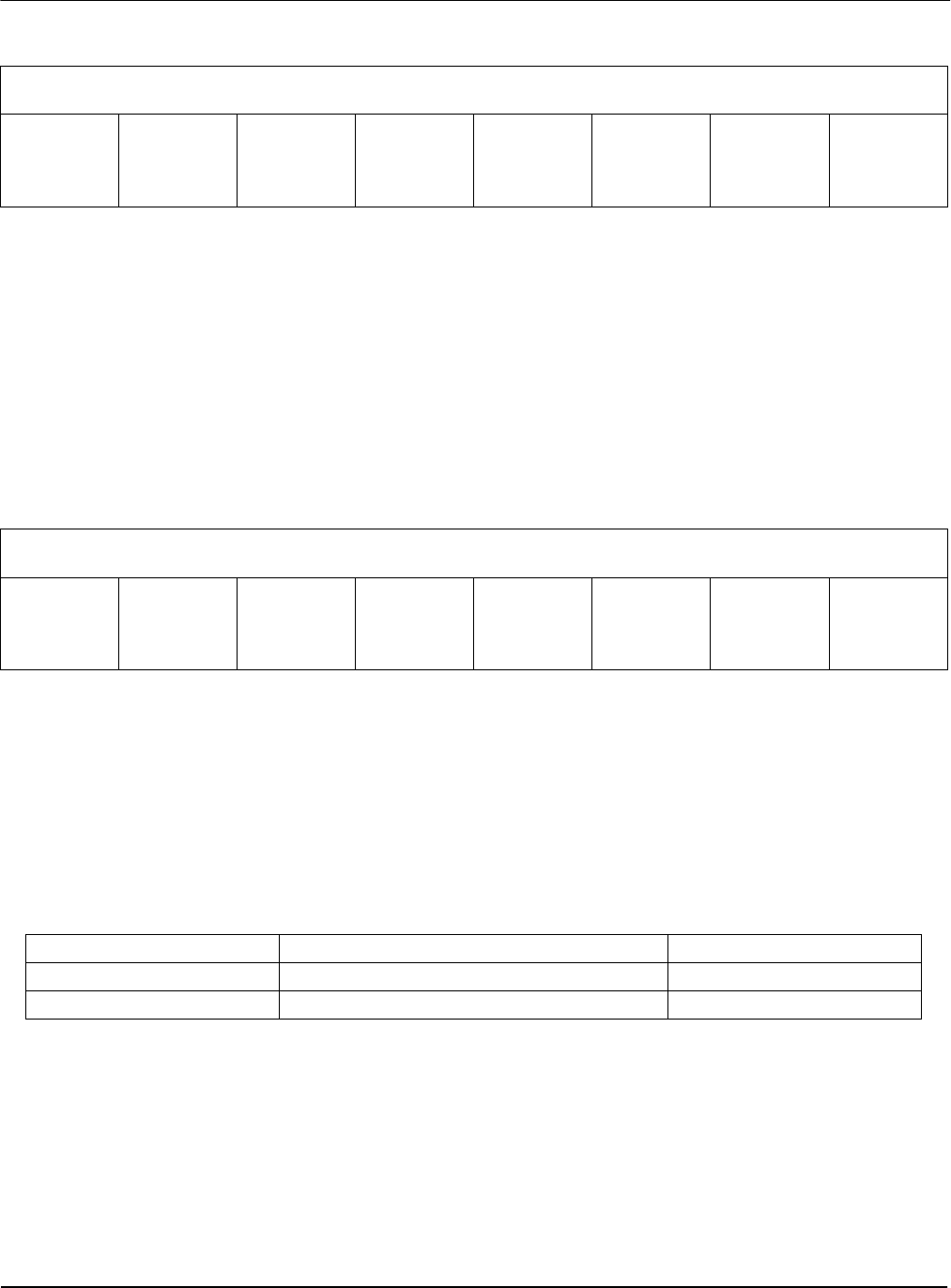

VRTC/FPFRAME Start Position Register

REG[0Bh] RW

n/a n/a

VRTC/

FPFRAME

Start Position

Bit 5

VRTC/

FPFRAME

Start Position

Bit 4

VRTC/

FPFRAME

Start Position

Bit 3

VRTC/

FPFRAME

Start Position

Bit 2

VRTC/

FPFRAME

Start Position

Bit 1

VRTC/

FPFRAME

Start Position

Bit 0

VRTC/FPFRAME Pulse Width Register

REG[0Ch] RW

VRTC Polarity

Select

FPFRAME

Polarity

Select

n/a n/a n/a

VRTC/

FPFRAME

Pulse Width

Bit 2

VRTC/

FPFRAME

Pulse Width

Bit 1

VRTC/

FPFRAME

Pulse Width

Bit 0

Table 8-5: FPFRAME Polarity Selection

FPFRAME Polarity Select Passive LCD FPFRAME Polarity TFT/D-TFD FPFRAME Polarity

0 active high active low

1 active low active high