Page 24

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

AB[16:13] I 115-118

CHi-Z

• For Philips PR31500/31700 Bus, these pins are connected to V

DD

.

• For Toshiba TX3912 Bus, these pins are connected to V

DD

.

• For PowerPC Bus, these pins input the system address bits 15

through 18 (A[15:18]).

• For all other busses, these pins input the system address bits 16

through 13 (A[16:13]).

See

“Host Bus Interface Pin Mapping”

for summary. See the respective

AC Timing diagram for detailed functionality.

AB17 I 114

CHi-Z

• For Philips PR31500/31700 Bus, this pin inputs the IO write

command (/CARDIOWR).

• For Toshiba TX3912 Bus, this pin inputs the IO write command

(CARDIOWR*).

• For PowerPC Bus, this pin inputs the system address bit 14 (A14).

• For all other busses, this pin inputs the system address bit 17 (A17).

See

“Host Bus Interface Pin Mapping”

for summary. See the respective

AC Timing diagram for detailed functionality.

AB18 I 113

CHi-Z

• For Philips PR31500/31700 Bus, this pin inputs the IO read

command (/CARDIORD).

• For Toshiba TX3912 Bus, this pin inputs the IO read command

(CARDIORD*).

• For PowerPC Bus, this pin inputs the system address bit 13 (A13).

• For all other busses, this pin inputs the system address bit 18 (A18).

See

“Host Bus Interface Pin Mapping”

for summary. See the respective

AC Timing diagram for detailed functionality.

AB19 I 112

CHi-Z

• For Philips PR31500/31700 Bus, this pin inputs the card control

register access (/CARDREG).

• For Toshiba TX3912 Bus, this pin inputs the card control register

(CARDREG*).

• For PowerPC Bus, this pin inputs the system address bit 12 (A12).

• For all other busses, this pin inputs the system address bit 19 (A19).

See

“Host Bus Interface Pin Mapping”

for summary. See the respective

AC Timing diagram for detailed functionality.

AB20 I 111

CHi-Z

• For the MIPS/ISA Bus, this pin inputs system address bit 20. Note

that for the ISA Bus, the unlatched LA20 must first be latched before

input to AB20.

• For Philips PR31500/31700 Bus, this pin inputs the address latch

enable (ALE).

• For Toshiba TX3912 Bus, this pin inputs the address latch enable

(ALE).

• For PowerPC Bus, this pin inputs the system address bit 11 (A11).

• For all other busses, this pin inputs the system address bit 20 (A20).

See

“Host Bus Interface Pin Mapping”

for summary. See the respective

AC Timing diagram for detailed functionality.

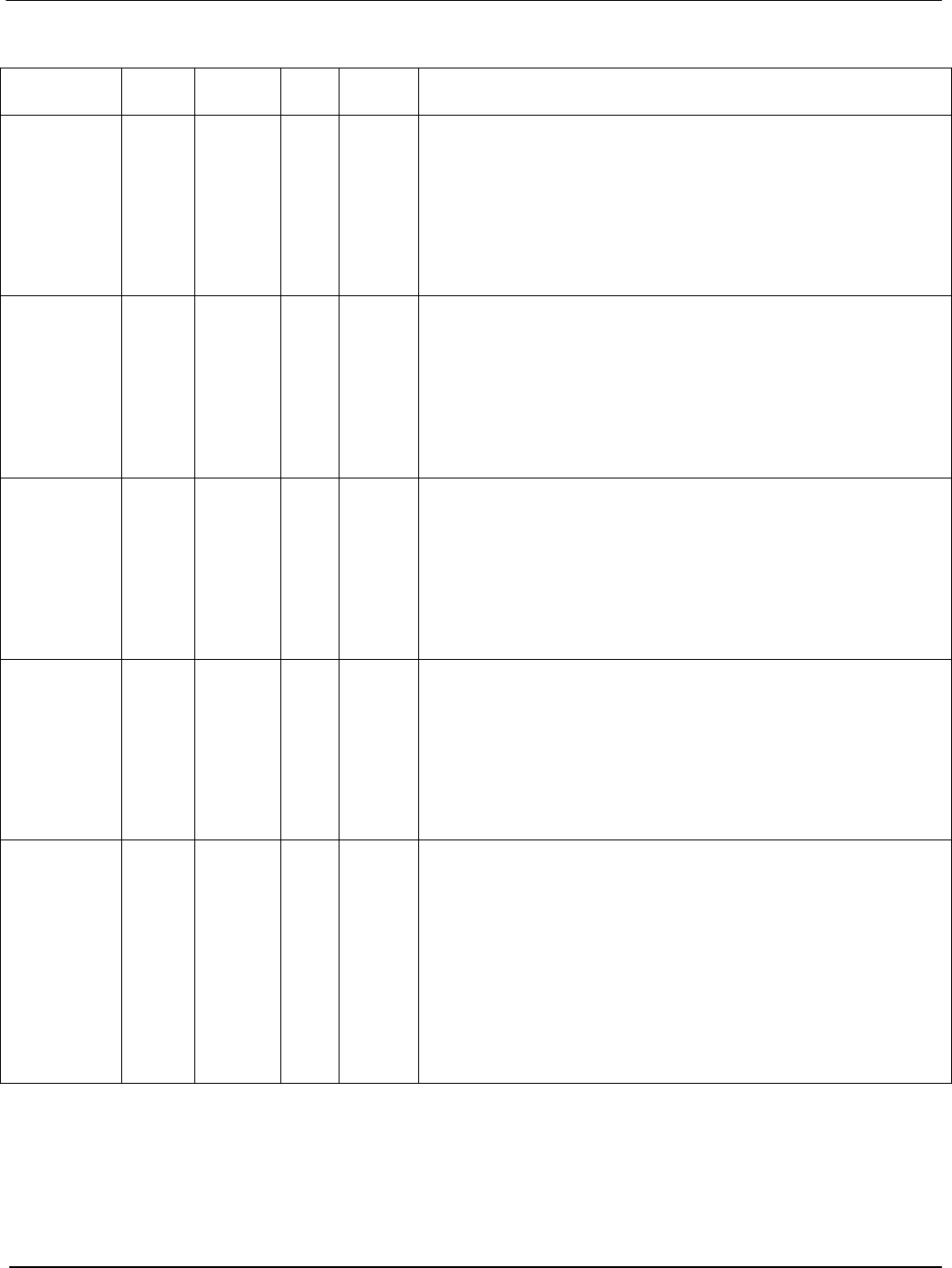

Table 5-1: Host Interface Pin Descriptions (Continued)

Pin Name Type Pin # Cell

RESET#

State

Description