Page 74

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

7.4 Power Sequencing

7.4.1 LCD Power Sequencing

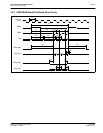

Figure 7-22: LCD Panel Power Off / Power On Timing. Drawn with LCDPWR set to active high polarity

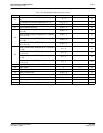

Table 7-21: LCD Panel Power Off/ Power On

Note

Where T

FPFRAME

is the period of FPFRAME and T

PCLK

is the period of the pixel clock.

Symbol Parameter Min Max Units

t1

SUSPEND# or LCD ENABLE BIT low to LCDPWR off

2T

FPFRAME

+

8T

PCLK

ns

t2

SUSPEND# or LCD ENABLE BIT low to FPFRAME inactive

1Frames

t3

FPFRAME inactive to FPLINE, FPSHIFT, FPDATA, DRDY inactive

128 Frames

t4

SUSPEND# to CLKI inactive

130 Frames

t5

SUSPEND# or LCD ENABLE BIT high to FPLINE, FPSHIFT,

FPDATA, DRDY active

T

FPFRAME

+

8T

PCLK

ns

t6

FPLINE, FPSHIFT, FPDATA, DRDY active to LCDPWR, on and

FPFRAME active

128 Frames

t7

CLKI active to SUSPEND# inactive

0ns

SUSPEND# or

LCDPWR

FPFRAME

FPLINE

FPSHIFT

FPDATA

DRDY

t1

t3

LCD Enable Bit

t4 t7

CLKI

t5 t6

t2