Epson Research and Development

Page 15

Vancouver Design Center

Interfacing to the Motorola MPC821 Microprocessor S1D13505

Issue Date: 01/02/05 X23A-G-008-05

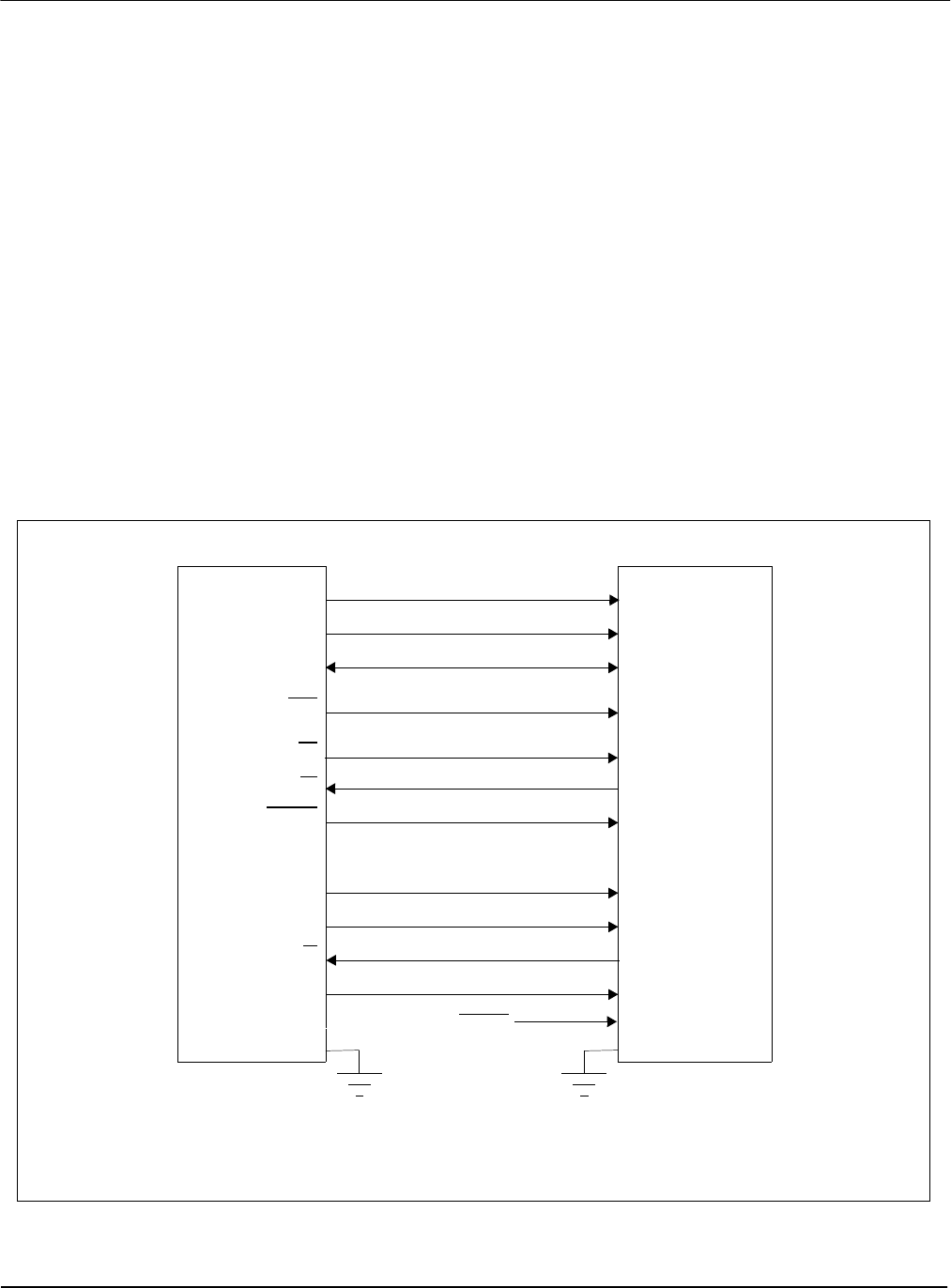

4 MPC821 to S1D13505 Interface

4.1 Hardware Description

The S1D13505 provides native Power PC bus support making it very simple to interface

the two devices. This application note describes both the environment necessary to connect

the S1D13505 to the MPC821 native system bus and the connection between the

S5U13505B00B Evaluation Board and the Motorola MPC821 Application Development

System (ADS).

Additionally, by implementing a dedicated display buffer, the S1D13505 can reduce

system power consumption, improve image quality, and increase system performance as

compared to the MPC821’s on-chip LCD controller.

The S1D13505, through the use of the MPC821 chip selects, can share the system bus with

all other MPC821 peripherals. The following figure demonstrates a typical implementation

of the S1D13505 to MPC821 interface.

Figure 4-1: Typical Implementation of MPC821 to S1D13505 Interface

MPC821 S1D13505

A[11:31]

D[0:15]

CS4

TA

RD/WR

TSIZ0

TSIZ1

SYSCLK

RESET

AB[20:0]

DB[15:0]

CS#

WAIT#

RD/WR#

RD#

WE0#

BUSCLK

RESET#

A10

M/R#

TS

BS#

WE1#BI

System

When connecting the S1D13505 RESET# pin, the system designer should be aware of all

conditions that may reset the S1D13505 (e.g. CPU reset can be asserted during wake-up

from power-down modes, or during debug states).

Note: